- Part: D4701A

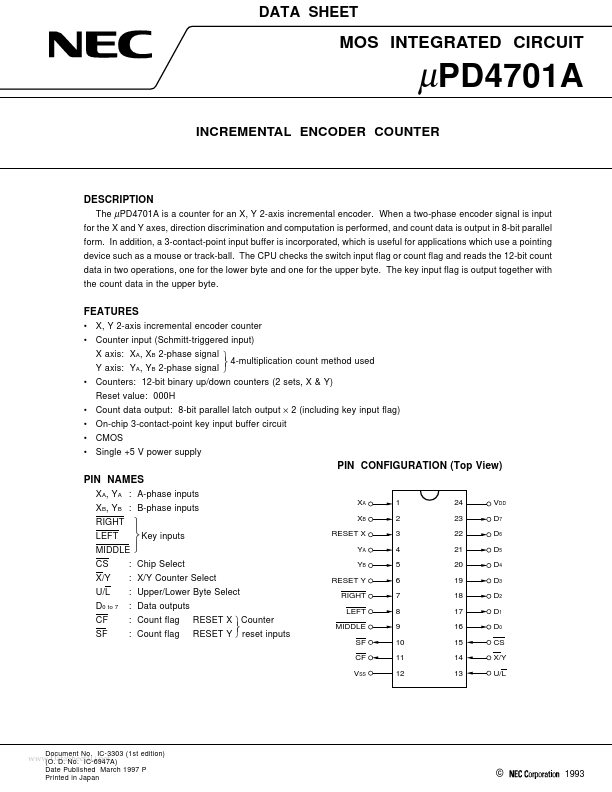

- Description: UPD4701A

- Manufacturer: NEC

- Size: 95.46 KB

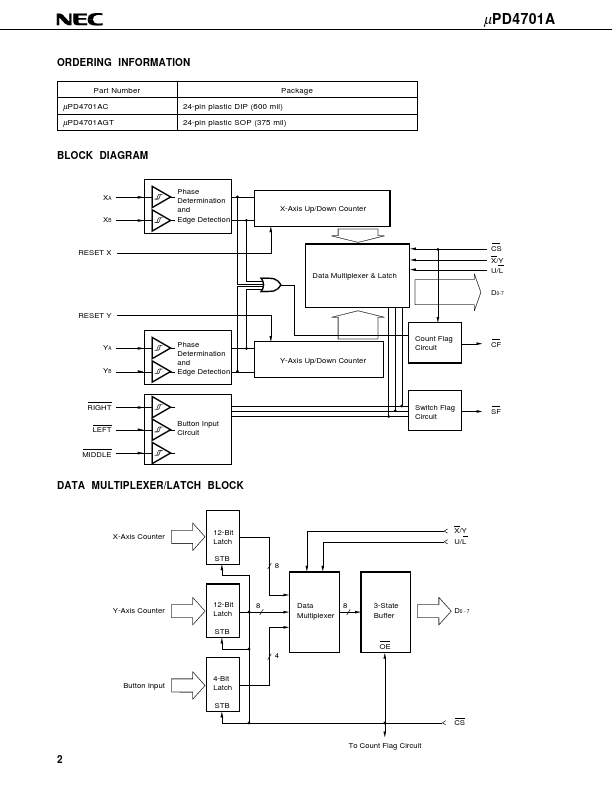

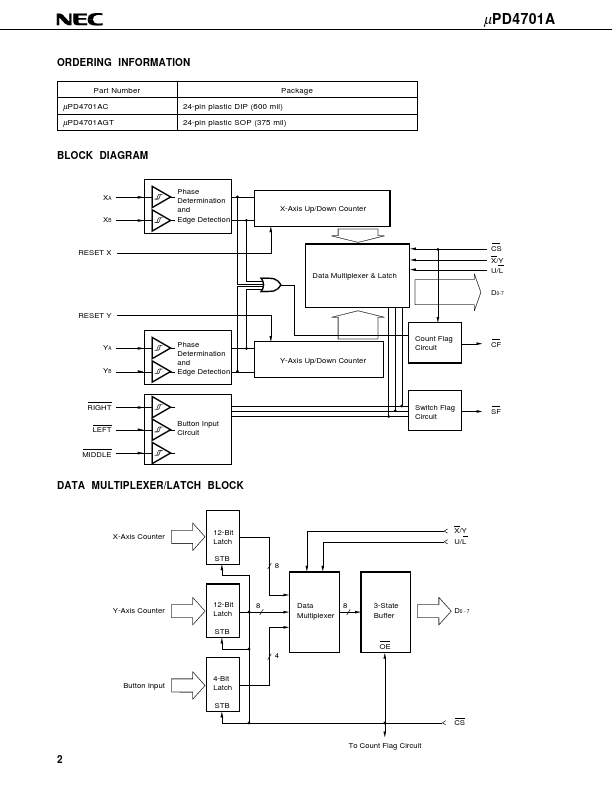

Page 2

Page 2

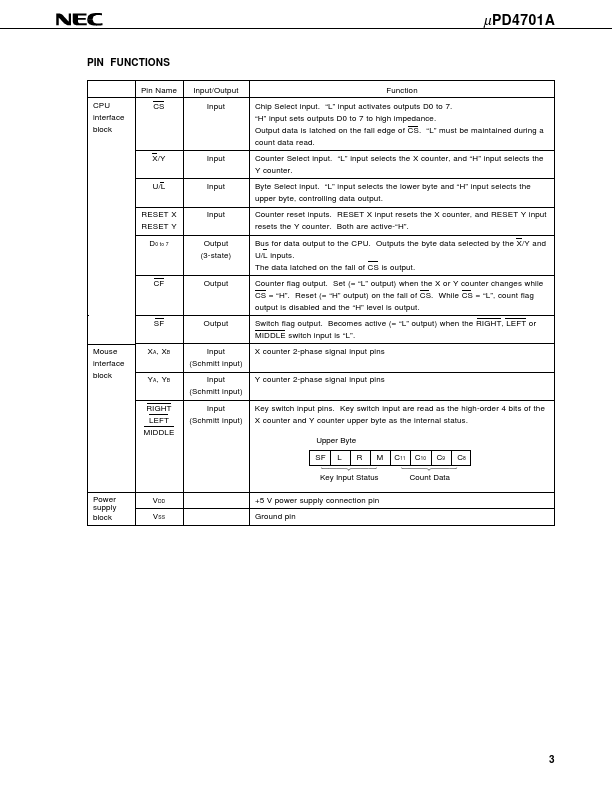

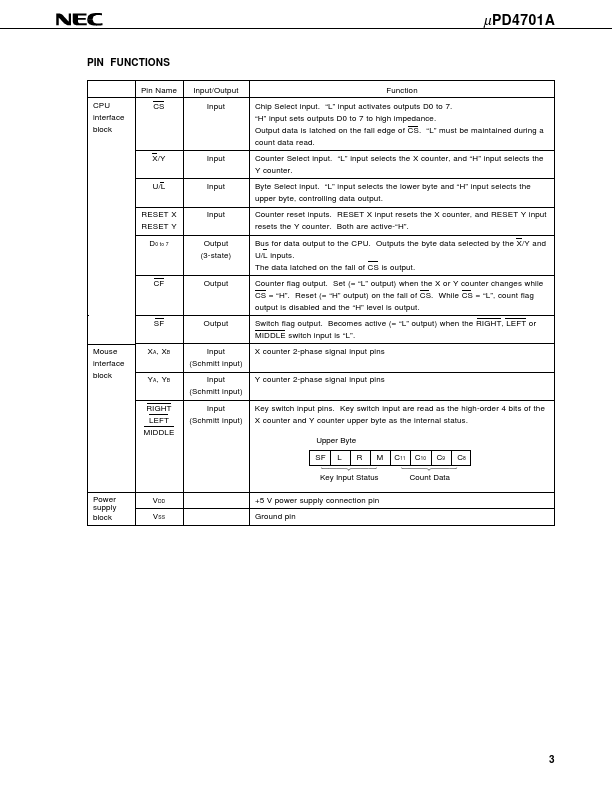

Page 3

Page 3

D4701A Key Features

- X, Y 2-axis incremental encoder counter

- Counter input (Schmitt-triggered input) X axis: XA, XB 2-phase signal 4-multiplication count method used Y axis: YA,

- Counters: 12-bit binary up/down counters (2 sets, X & Y) Reset value: 000H

- Count data output: 8-bit parallel latch output × 2 (including key input flag)

- On-chip 3-contact-point key input buffer circuit

- Single +5 V power supply

Related NEC Datasheets

| Part Number |

Description |

|

D4723GS

|

UPD4723GS |