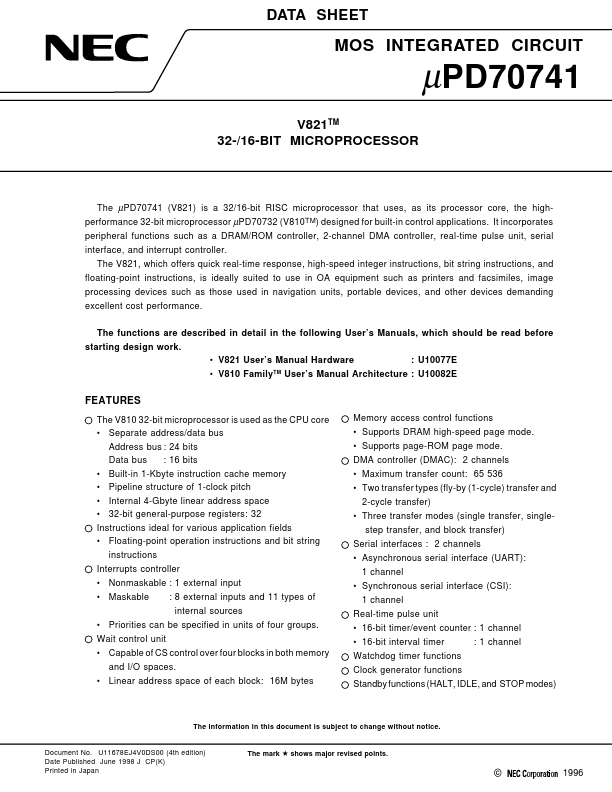

UPD70741

Overview

- Separate address/data bus Address bus : 24 bits Data bus : 16 bits

- Built-in 1-Kbyte instruction cache memory

- Pipeline structure of 1-clock pitch

- Internal 4-Gbyte linear address space

- 32-bit general-purpose registers: 32 Instructions ideal for various application fields

- Floating-point operation instructions and bit string instructions Interrupts controller

- Nonmaskable : 1 external input

- Maskable : 8 external inputs and 11 types of internal sources

- Priorities can be specified in units of four groups. Wait control unit

- Capable of CS control over four blocks in both memory and I/O spaces.