P2503HVG Description

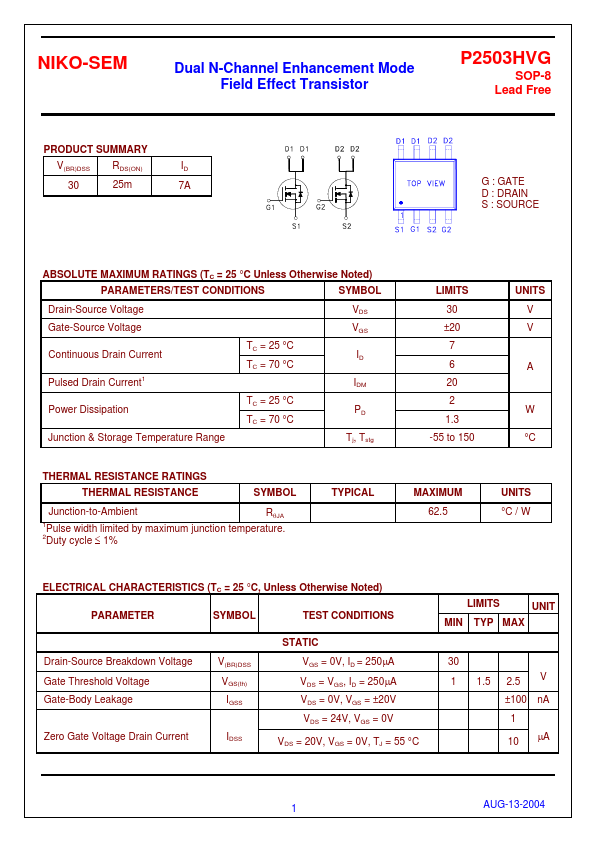

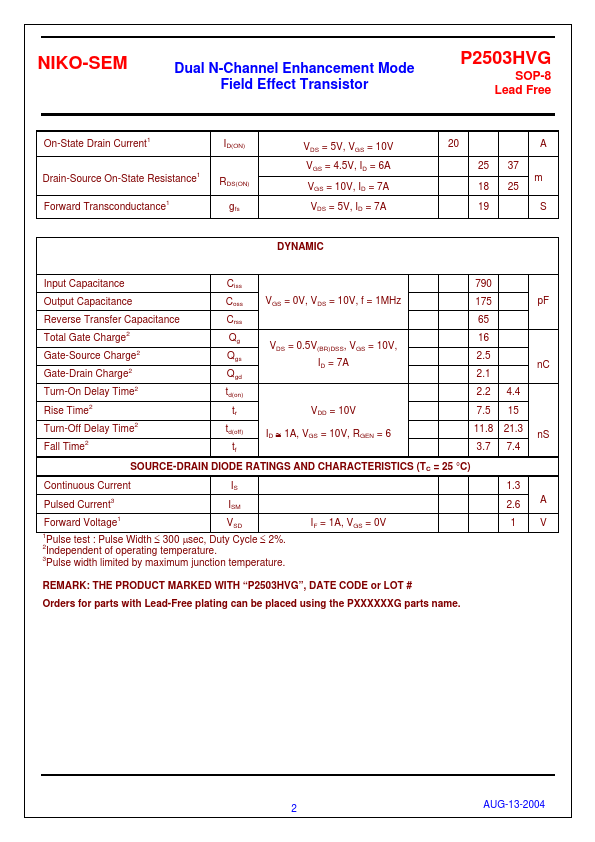

NIKO-SEM Dual N-Channel Enhancement Mode Field Effect Transistor P2503HVG SOP-8 Lead Free PRODUCT SUMMARY V(BR)DSS RDS(ON) 30 25m ID 7A G : SOURCE RATINGS (TC = 25 °C Unless Otherwise Noted) PARAMETERS/TEST CONDITIONS SYMBOL Drain-Source Voltage Gate-Source Voltage Continuous Drain Current Pulsed Drain Current1 Power Dissipation Junction & Storage Temperature Range TC = 25 °C TC = 70 °C TC = 25 °C TC = 70 °C VDS VGS...