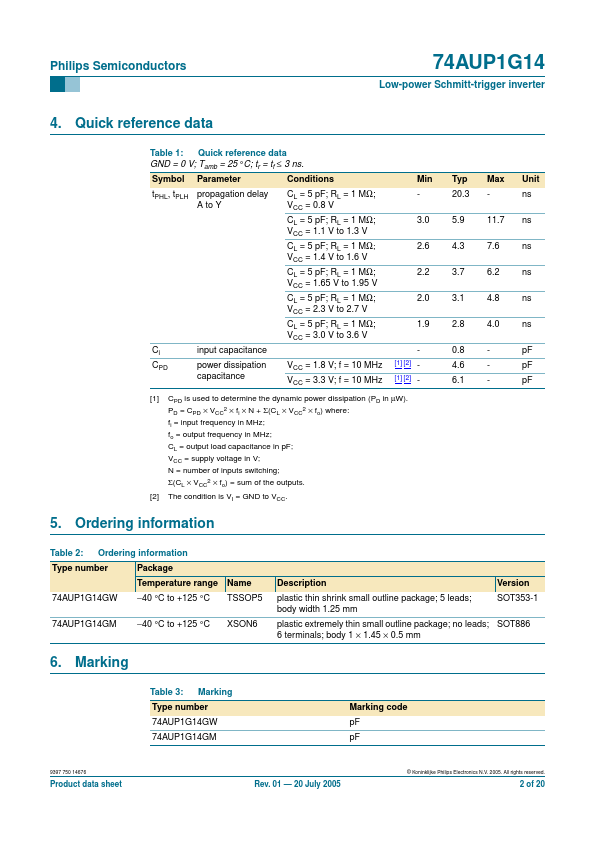

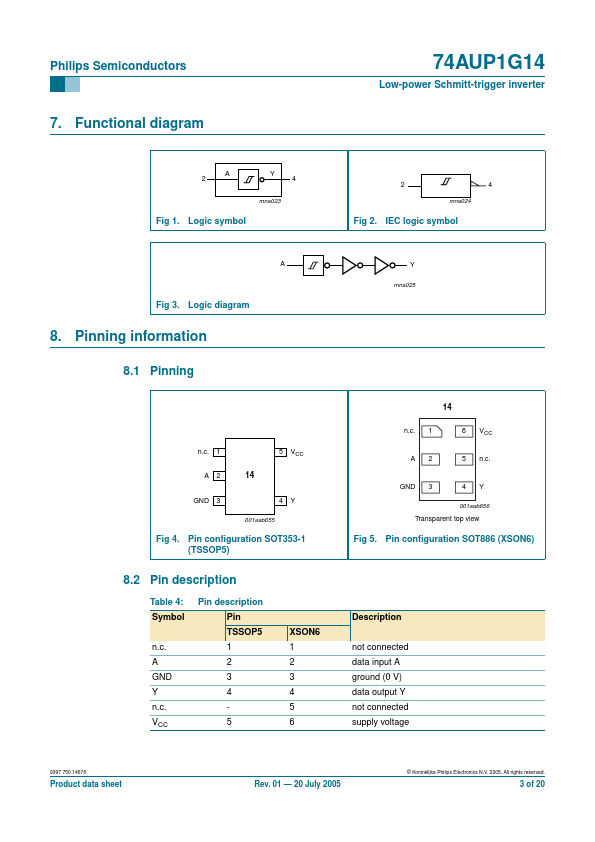

- Part: 74AUP1G14

- Description: Low-power Schmitt-trigger inverter

- Manufacturer: NXP Semiconductors

- Size: 144.37 KB

Other 74AUP1G14 Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

Diodes Incorporated

Diodes Incorporated |

74AUP1G14 | SINGLE SCHMITT-TRIGGER INVERTER |

Nexperia

Nexperia |

74AUP1G14 | Low-power Schmitt trigger inverter |