74AUP1G14

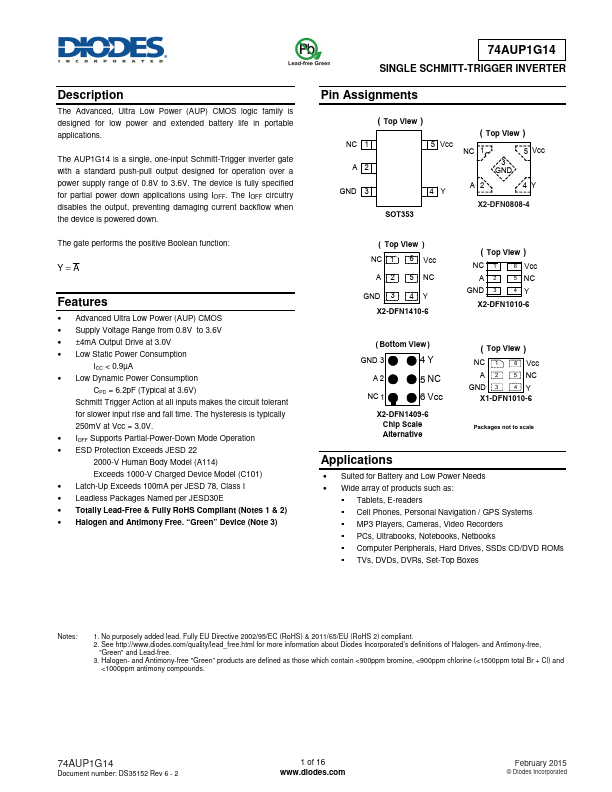

74AUP1G14 is SINGLE SCHMITT-TRIGGER INVERTER manufactured by Diodes Incorporated.

Description

The Advanced, Ultra Low Power (AUP) CMOS logic family is designed for low power and extended battery life in portable applications.

The AUP1G14 is a single, one-input Schmitt-Trigger inverter gate with a standard push-pull output designed for operation over a power supply range of 0.8V to 3.6V. The device is fully specified for partial power down applications using IOFF. The IOFF circuitry disables the output, preventing damaging current backflow when the device is powered down.

The gate performs the positive Boolean function:

Y=A

Features

- Advanced Ultra Low Power (AUP) CMOS

- Supply Voltage Range from 0.8V to 3.6V

- ±4mA Output Drive at 3.0V

- Low Static Power...