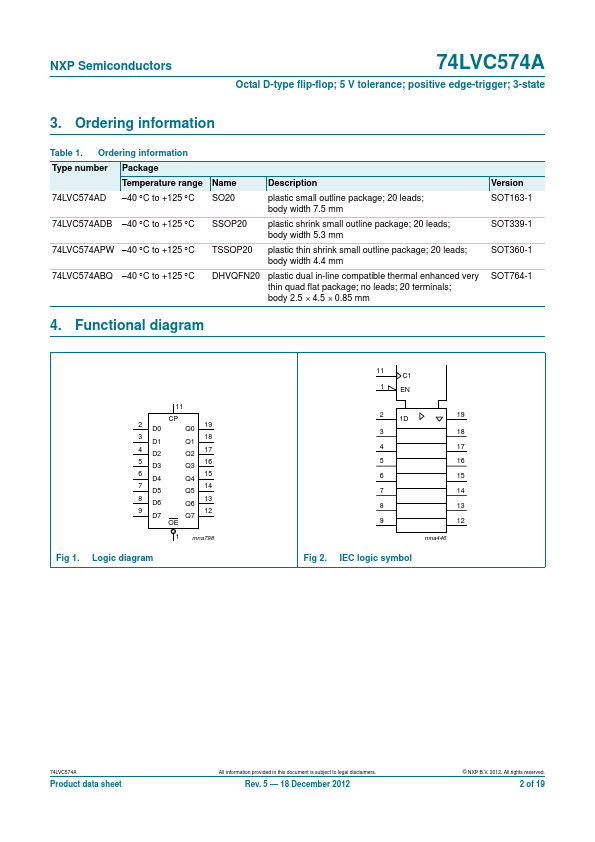

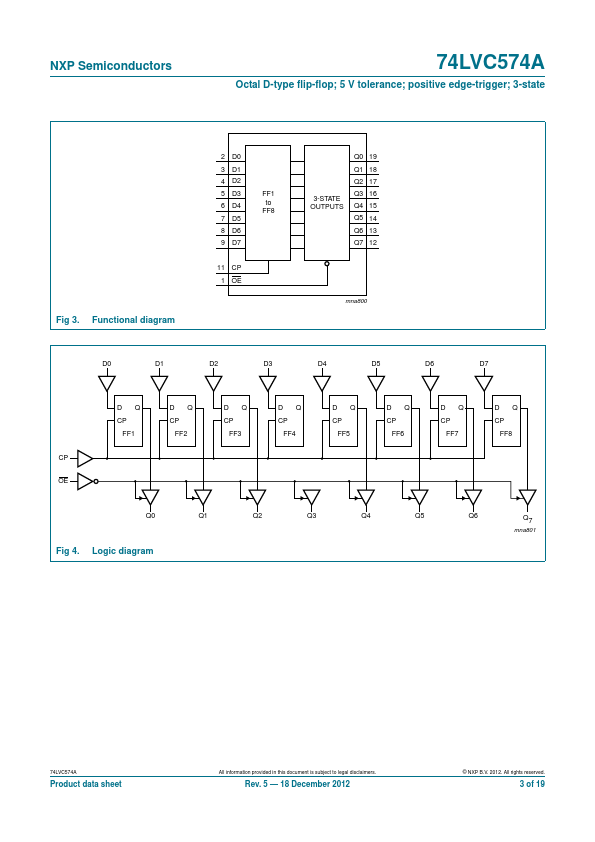

- Part: 74LVC574A

- Description: Octal D-type flip-flop

- Manufacturer: NXP Semiconductors

- Size: 136.42 KB

Other 74LVC574A Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

Nexperia

Nexperia |

74LVC574A | Octal D-type flip-flop |

Diodes Incorporated

Diodes Incorporated |

74LVC574A | OCTAL D-TYPE FLIP-FLOP |

| 74LVC574A | Low-Voltage CMOS Octal D-Type Flip-Flop |