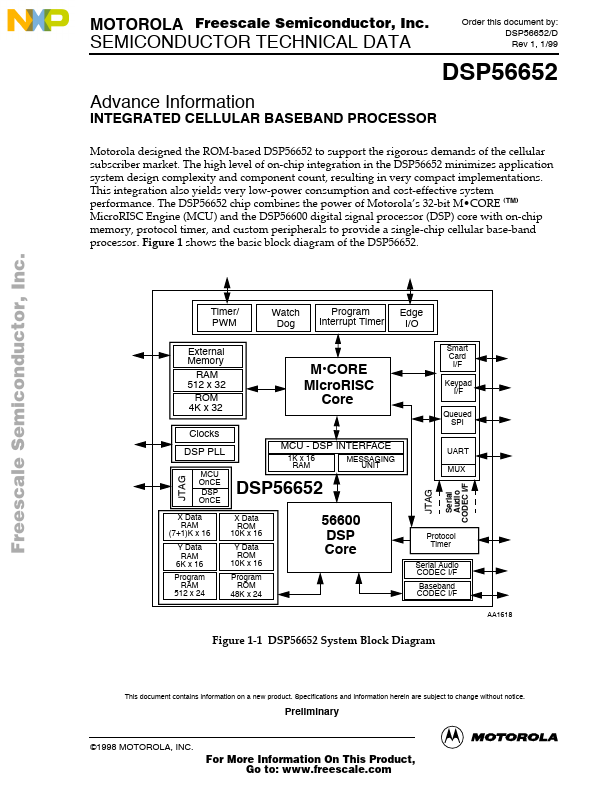

DSP56652

FEATURES

DSP56652 Features

RISC M- CORE MCU

- 32-bit load/store RISC architecture

- Fixed 16-bit instruction length

- 16-entry 32-bit general-purpose register file

- 32-bit internal address and data buses

- Efficient four-stage, fully interlocked execution pipeline

- Single-cycle execution for most instructions, two cycles for branches and memory accesses

- Special branch, byte, and bit manipulation instructions

- Support for byte, half-word, and word memory accesses

- Fast interrupt support via vectoring/auto-vectoring and a 16-entry dedicated alternate register file

High Performance DSP56600 Core

- 1 ´ engine (e.g., 70 MHz = 70 MIPS)

- Fully pipelined 16 ´ 16-bit parallel multiplier-accumulator (MAC)

- Two...