Datasheet Summary

MOTOROLA Freescale Semiconductor, Inc.

SEMICONDUCTOR TECHNICAL DATA

Order this document by: DSP56651/D Rev 0, 6/98

Advance Information

INTEGRATED CELLULAR BASEBAND PROCESSOR

DEVELOPMENT IC

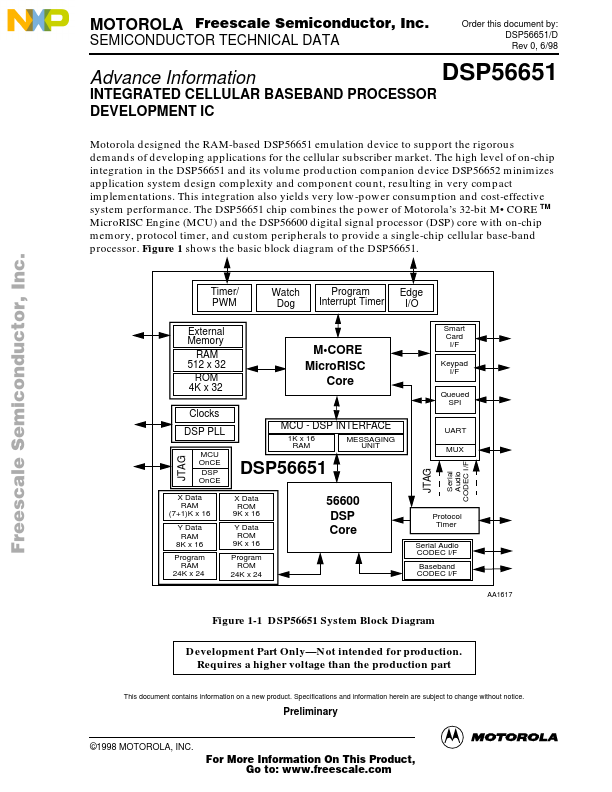

Motorola designed the RAM-based DSP56651 emulation device to support the rigorous demands of developing applications for the cellular subscriber market. The high level of on-chip integration in the DSP56651 and its volume production panion device DSP56652 minimizes application system design plexity and ponent count, resulting in very pact implementations. This integration also yields very low-power consumption and cost-effective system performance. The DSP56651 chip bines...