MPC5748G

Overview

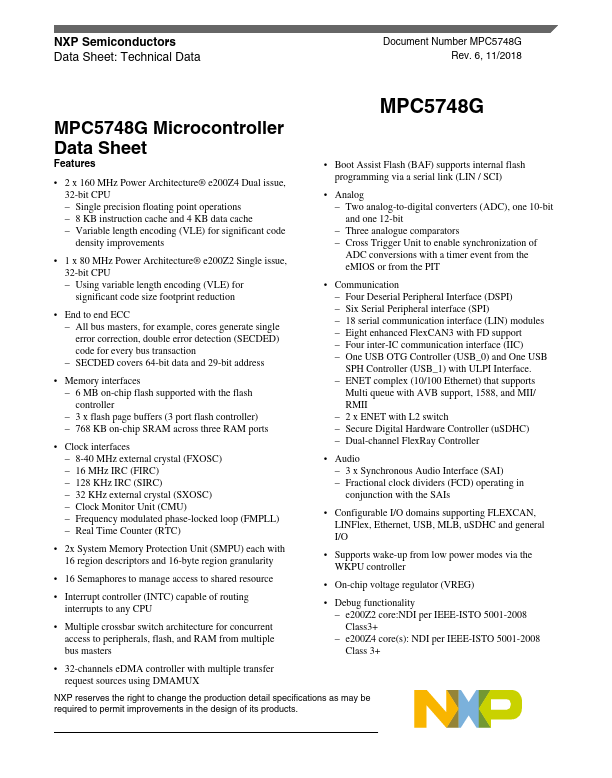

- 2 x 160 MHz Power Architecture® e200Z4 Dual issue, 32-bit CPU - Single precision floating point operations - 8 KB instruction cache and 4 KB data cache - Variable length encoding (VLE) for significant code density improvements

- 1 x 80 MHz Power Architecture® e200Z2 Single issue, 32-bit CPU - Using variable length encoding (VLE) for significant code size footprint reduction

- End to end ECC - All bus masters, for example, cores generate single error correction, double error detection (SECDED) code for every bus transaction - SECDED covers 64-bit data and 29-bit address

- Memory interfaces - 6 MB on-chip flash supported with the flash controller - 3 x flash page buffers (3 port flash controller) - 768 KB on-chip SRAM across three RAM ports

- Clock interfaces - 8-40 MHz external crystal (FXOSC) - 16 MHz IRC (FIRC) - 128 KHz IRC (SIRC) - 32 KHz external crystal (SXOSC) - Clock Monitor Unit (CMU) - Frequency modulated phase-locked loop (FMPLL) - Real Time Counter (RTC)

- 2x System Memory Protection Unit (SMPU) each with 16 region descriptors and 16-byte region granularity

- 16 Semaphores to manage access to shared resource

- Interrupt controller (INTC) capable of routing interrupts to any CPU

- Multiple crossbar switch architecture for concurrent access to peripherals, flash, and RAM from multiple bus masters MPC5748G

- Boot Assist Flash (BAF) supports internal flash programming via a serial link (LIN / SCI)