74LVC2G74 Description

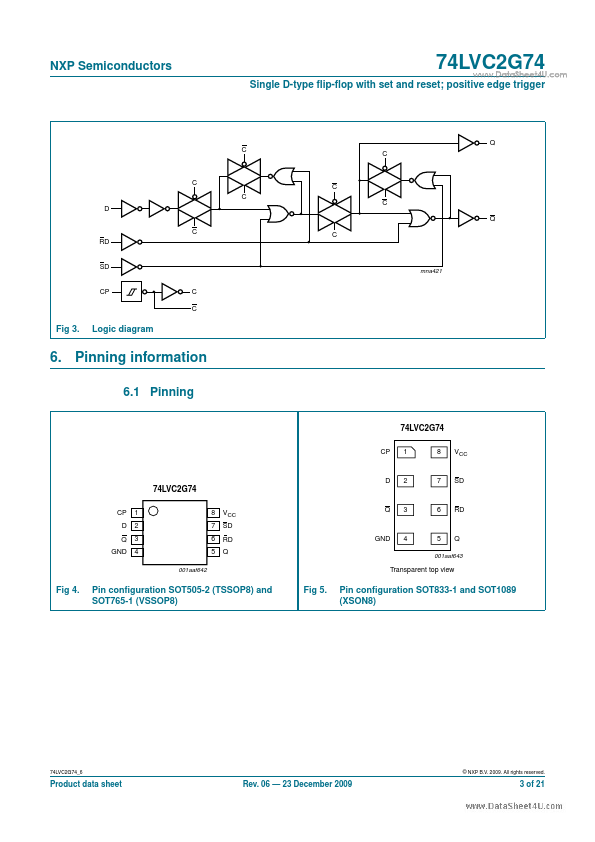

The 74LVC2G74 is a single positive-edge triggered D-type flip-flop with individual data (D) inputs, clock (CP) inputs, set (SD) and reset (RD) inputs, and plementary Q and Q outputs. This device is fully specified for partial power-down applications using IOFF. The IOFF circuitry disables the output, preventing damaging backflow current through the device when it is powered down.