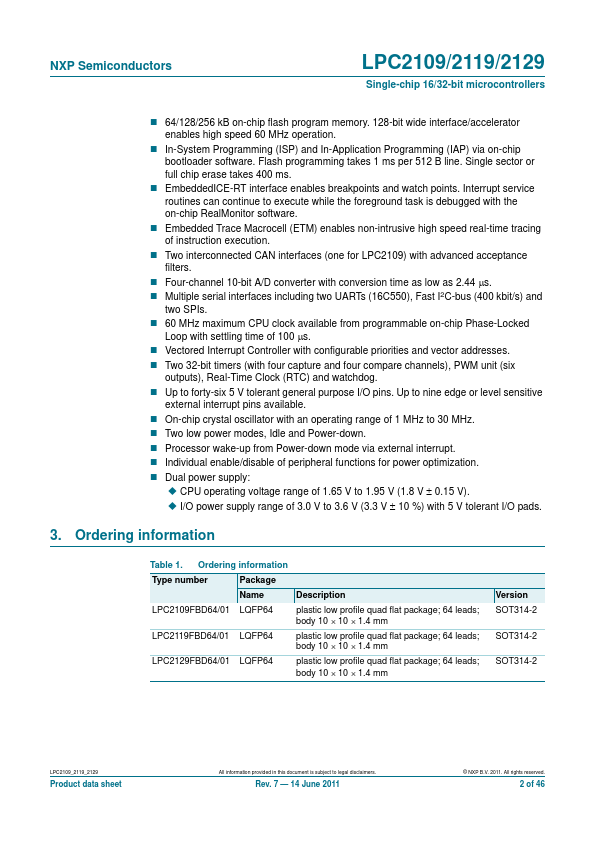

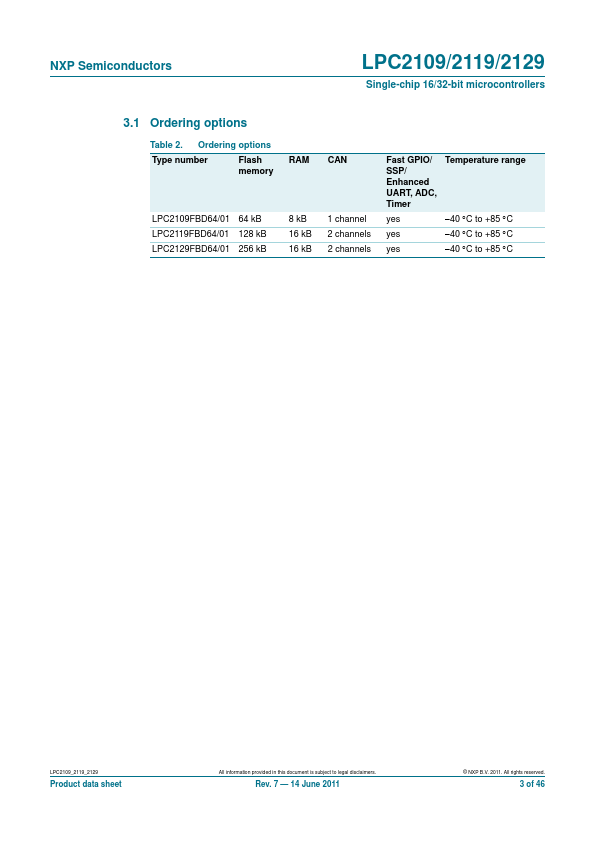

- Part: LPC2129

- Description: Single-chip 16/32-bit microcontrollers

- Manufacturer: NXP Semiconductors

- Size: 260.36 KB

Related NXP Semiconductors Datasheets

| Part Number | Description |

|---|---|

| LPC2124 | Single-chip 16/32-bit microcontrollers |

| LPC2109 | Single-chip 16/32-bit microcontrollers |

| LPC2114 | Single-chip 16/32-bit microcontrollers |

| LPC2119 | Single-chip 16/32-bit microcontrollers |

| LPC2157 | Single-chip 16-bit/32-bit microcontrollers; 512 kB fash |