74F413

Overview

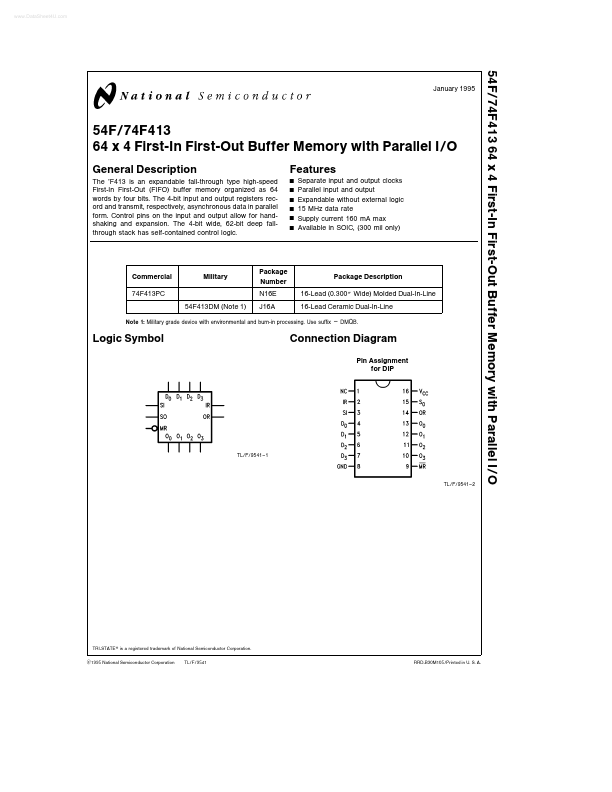

The ’F413 is an expandable fall-through type high-speed First-In First-Out (FIFO) buffer memory organized as 64 words by four bits The 4-bit input and output registers record and transmit respectively asynchronous data in parallel form Control pins on the input and output allow for handshaking and expansion The 4-bit wide 62-bit deep fallthrough stack has self-contained control logic.