- Part: 54ACT825

- Manufacturer: National Semiconductor

- Size: 186.10 KB

Related National Semiconductor Datasheets

| Part Number | Description |

|---|---|

| 54ACT821 | 10-Bit D Flip-Flop |

| 54ACT823 | 9-Bit D Flip-Flop |

| 54ACT818 | 8-Bit Diagnostic Register |

| 54ACT899 | 9-Bit Latchable Transceiver |

| 54ACT00 | Quad 2-Input NAND Gate |

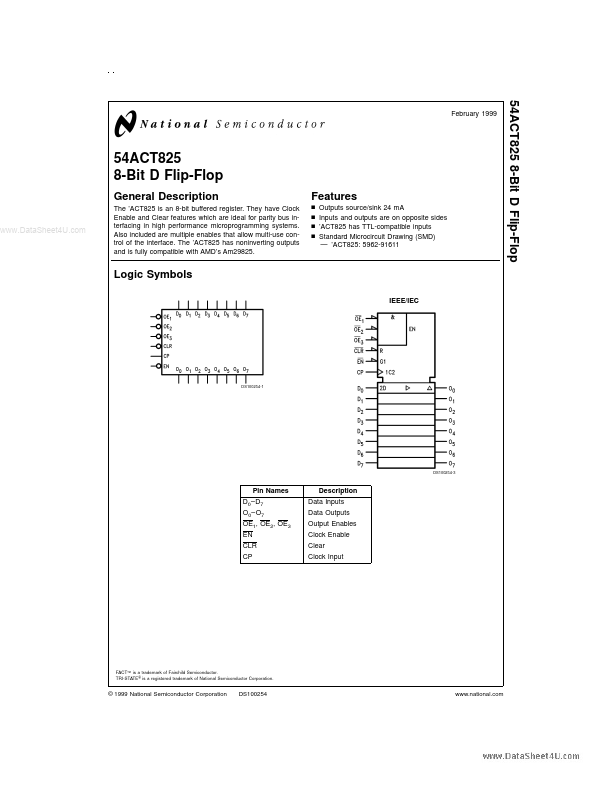

54ACT825 Description

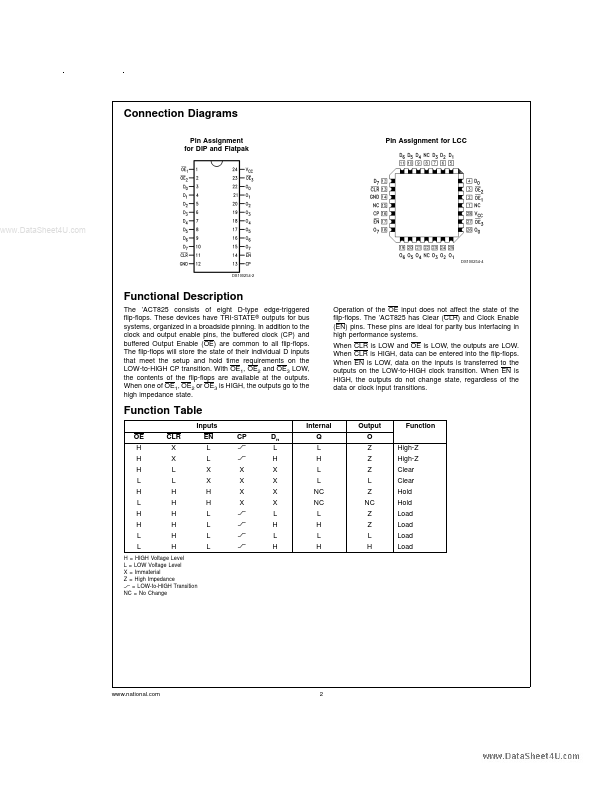

The ’ACT825 is an 8-bit buffered register. They have Clock Enable and Clear.