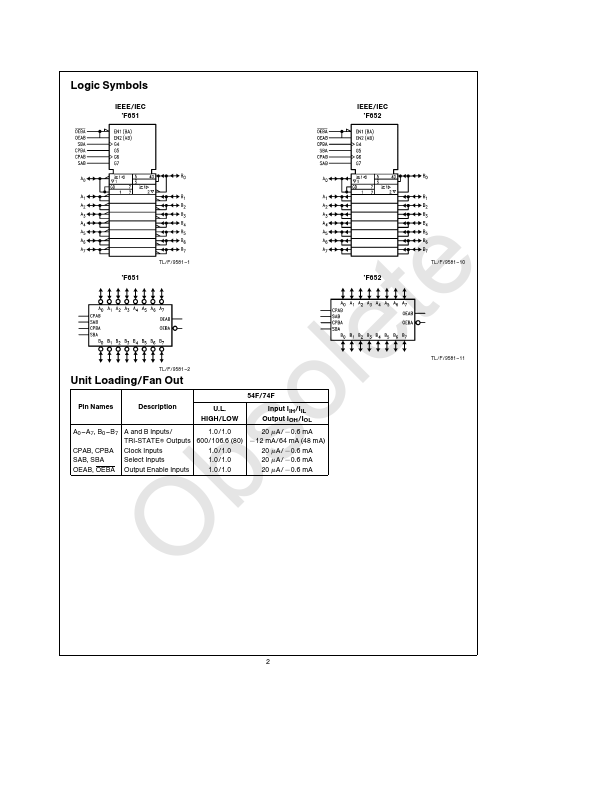

Datasheet Summary

54F 74F651 54F 74F652 Transceivers Registers

Obsolete

December 1994

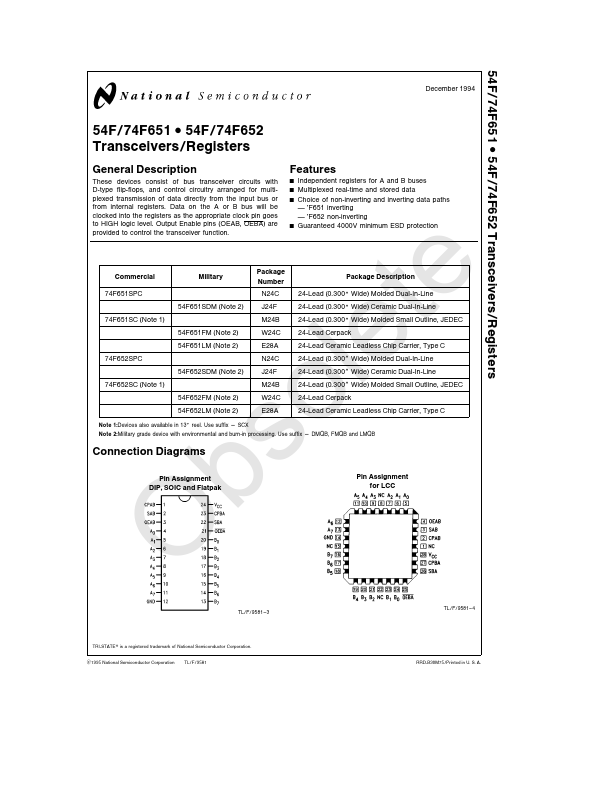

54F 74F651 54F 74F652

Transceivers Registers

General Description

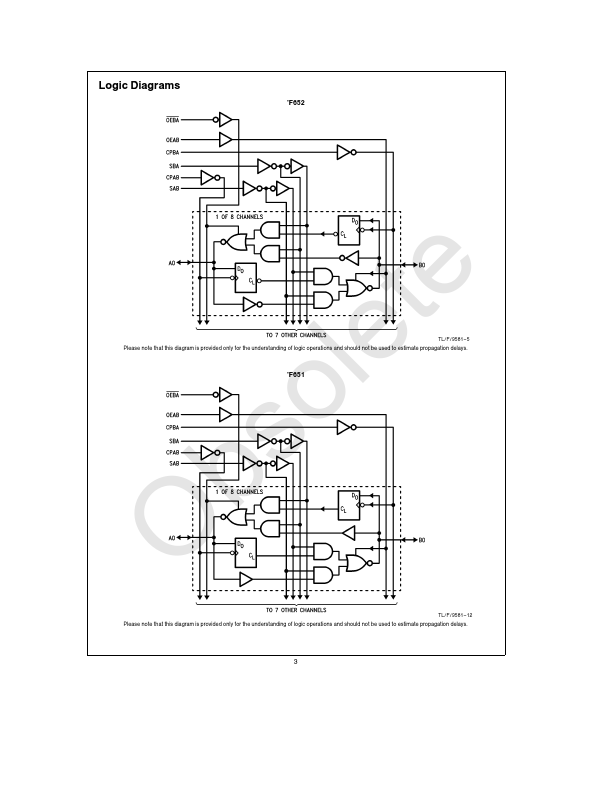

These devices consist of bus transceiver circuits with D-type flip-flops and control circuitry arranged for multiplexed transmission of data directly from the input bus or from internal registers Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to HIGH logic level Output Enable pins (OEAB OEBA) are provided to control the transceiver function

Features

Y Independent registers for A and B buses Y Multiplexed real-time and stored data Y Choice of non-inverting and inverting data paths

’F651 inverting ’F652...