54FCT377

54FCT377 is Octal D-Type Flip-Flop manufactured by National Semiconductor.

54FCT377 Octal D-Type Flip-Flop with Clock Enable

October 1999

54FCT377 Octal D-Type Flip-Flop with Clock Enable

General Description

The ’FCT377 has eight edge-triggered, D-type flip-flops with individual D inputs and Q outputs. The mon buffered Clock (CP) input loads all flip-flops simultaneously, when the Clock Enable (CE) is LOW.

The register is fully edge-triggered. The state of each D input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop’s Q output. The CE input must be stable only one setup time prior to the LOW-to-HIGH clock transition for predictable operation.

Features n Clock enable for address and data synchronization applications n Eight edge-triggered D flip-flops n Buffered mon clock n See ’FCT273 for master reset version n See ’FCT373 for transparent latch version n See ’FCT374 for TRI-STATE® version n TTL input and output level patible n CMOS power consumption n Output sink capability of 32 m A, source capability of

12 m A n Standard Microcircuit Drawing (SMD) 5962-8762701

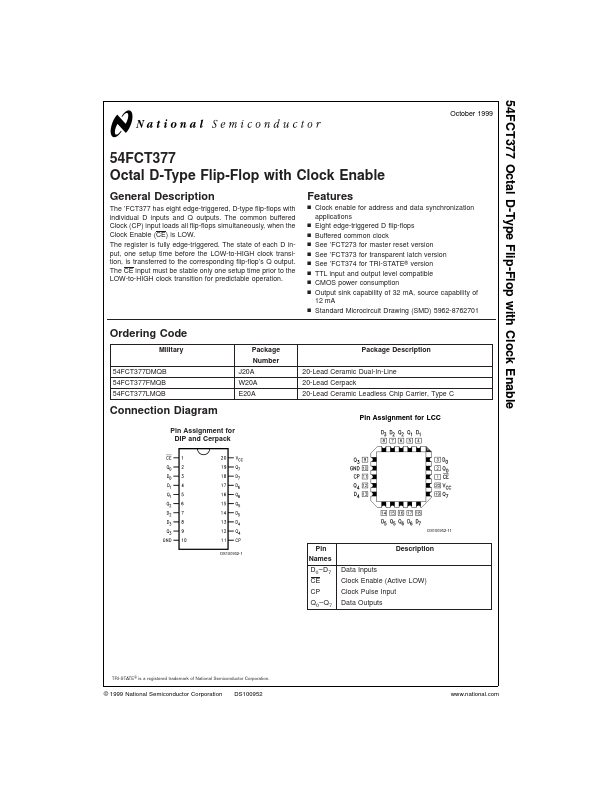

Ordering Code

Military

54FCT377DMQB 54FCT377FMQB 54FCT377LMQB

Connection Diagram

Package Number J20A W20A E20A

Pin Assignment for DIP and Cerpack

Package Description

20-Lead Ceramic Dual-In-Line 20-Lead Cerpack 20-Lead Ceramic Leadless Chip Carrier, Type C

Pin Assignment for LCC

DS100952-1

DS100952-11

Pin Names D0- D7 CE CP Q0- Q7

Description

Data Inputs Clock Enable (Active LOW) Clock Pulse Input Data Outputs

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation DS100952

.national.

Truth Table Logic Diagram

Mode Select-Function Table

Operating Mode Load “1”

Inputs CP CE...