54FCT573

54FCT573 is Octal D-Type Latch manufactured by National Semiconductor.

54FCT573 Octal D-Type Latch with TRI-STATE Outputs

August 1998

54FCT573 Octal D-Type Latch with TRI-STATE® Outputs

General Description

The ’FCT573 is an octal latch with buffered mon Latch Enable (LE) and buffered mon Output Enable (OE) inputs.

This device is functionally identical to the ’FCT373 but has different pinouts.

Features n Inputs and outputs on opposite sides of package allow easy interface with microprocessors n Useful as input or output port for microprocessors n TTL input and output level patible n CMOS power consumption n Functionally identical to ’FCT373 n TRI-STATE outputs for bus interfacing n Output sink capability of 32 m A, source capability of

12 m A n Standard Microcircuit Drawing (SMD) 5962-8863901

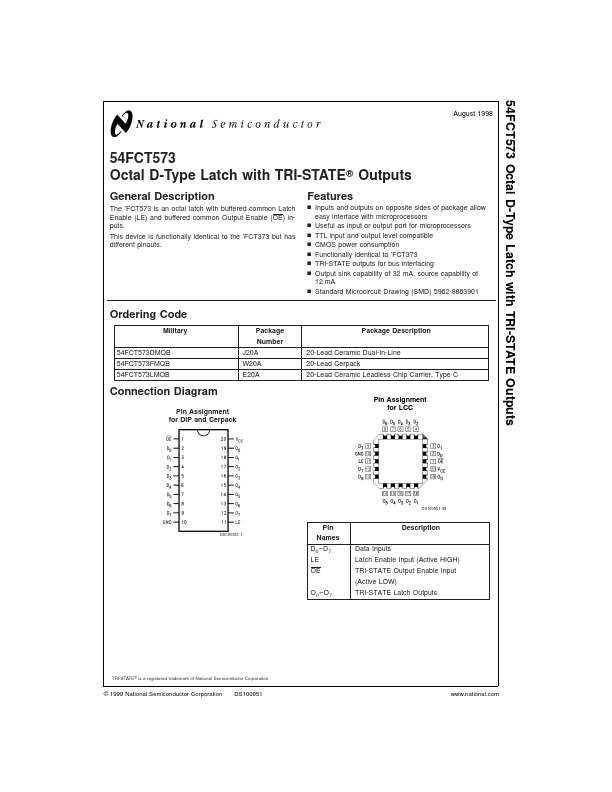

Ordering Code

Military

54FCT573DMQB 54FCT573FMQB 54FCT573LMQB

Connection Diagram

Package Number J20A W20A E20A

Pin Assignment for DIP and Cerpack

Package Description

20-Lead Ceramic Dual-In-Line 20-Lead Cerpack 20-Lead Ceramic Leadless Chip Carrier, Type C

Pin Assignment for LCC

DS100951-1

Pin Names D0- D7 LE OE

O0- O7

DS100951-39

Description

Data Inputs Latch Enable Input (Active HIGH) TRI-STATE Output Enable Input (Active LOW) TRI-STATE Latch Outputs

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation DS100951

.national.

Functional Description

The ’FCT573 contains eight D-type latches with TRI-STATE output buffers. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE. The TRI-STATE buffers are controlled by the Output Enable (OE) input. When OE is LOW, the buffers are in the bi-state mode. When OE is HIGH the buffers are in the high impedance mode but this does...