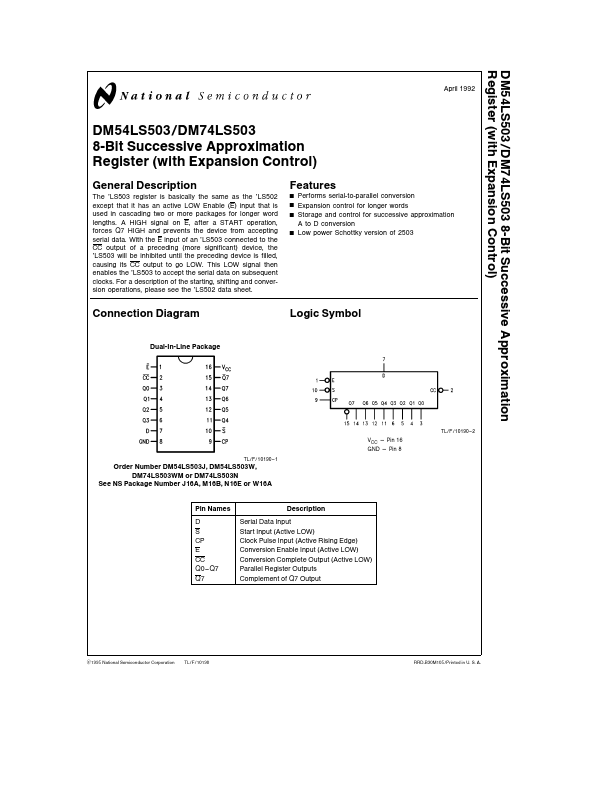

- Part: 54LS503

- Description: 8-Bit Successive Approximation Register

- Manufacturer: National Semiconductor

- Size: 126.36 KB

Related National Semiconductor Datasheets

| Part Number | Description |

|---|---|

| 54LS00 | Quad 2-Input NAND Gates |

| 54LS02 | Quad 2-Input NOR Gates |

| 54LS03 | Quad 2-Input NAND Gates |

| 54LS04 | Hex Inverting Gates |

| 54LS05 | HEX INVERTERS |