CGS64C800-NationalSemiconductor.pdf

Datasheet Details

Part number:

CGS64C801, CGS64C800

Manufacturer:

National Semiconductor

File Size:

402.18 KB

Description:

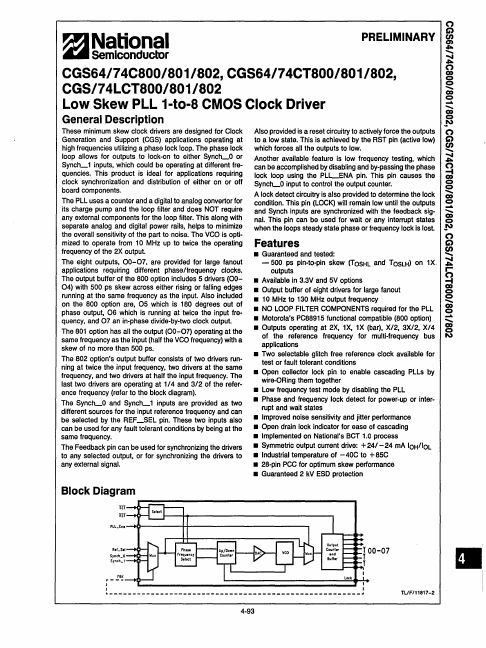

Low skew pll 1-to-8 cmos clock driver.

Note:

This datasheet PDF includes multiple part numbers: CGS64C801, CGS64C800.

Please refer to the document for exact specifications by model.