DM54LS132

DM54LS132 is NAND Gates manufactured by National Semiconductor.

DM54LS132 DM74LS132 Quad 2-Input NAND Gates with Schmitt Trigger Inputs

DM54LS132 DM74LS132 Quad 2-Input NAND Gates with Schmitt Trigger Inputs

General Description

This device contains four independent gates each of which performs the logic NAND function Each input has hysteresis which increases the noise immunity and transforms a slowly changing input signal to a fast changing jitter free output

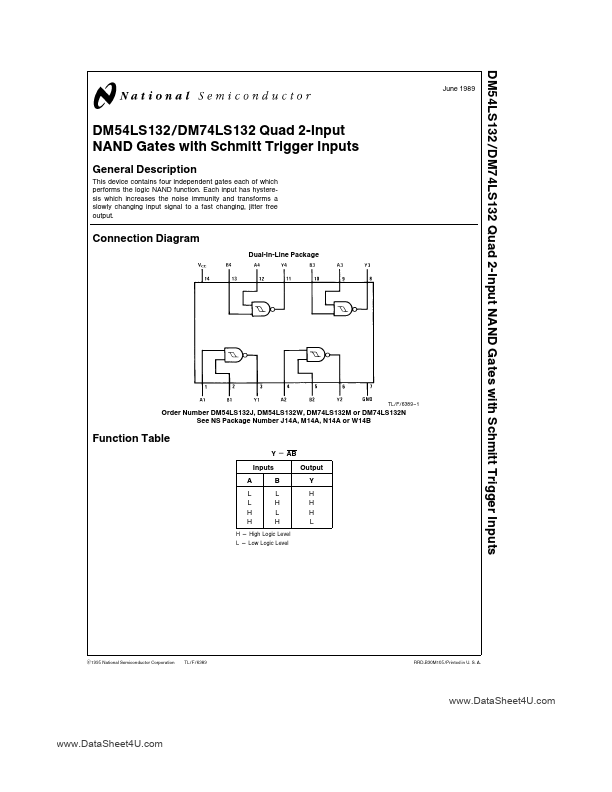

Connection Diagram

Dual-In-Line Package

June 1989

TL F 6389

- 1

Order Number DM54LS132J DM54LS132W DM74LS132M or DM74LS132N See NS Package Number J14A M14A N14A or W14B

Function Table

Y e AB

Inputs

Output

H e High Logic Level L e Low Logic Level

C1995 National Semiconductor Corporation TL F 6389

..

RRD-B30M105 Printed in U S...