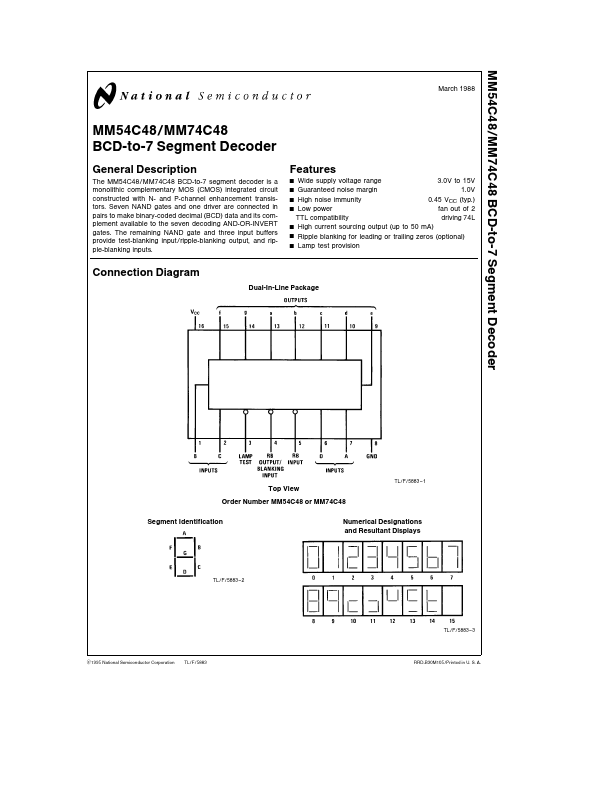

MM74C48 Overview

The MM54C48 MM74C48 BCD-to-7 segment decoder is a monolithic plementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors Seven NAND gates and one driver are connected in pairs to make binary-coded decimal (BCD) data and its plement available to the seven decoding AND-OR-INVERT gates The remaining NAND gate and three input buffers provide test-blanking input ripple-blanking...