MSM54V25632A Description

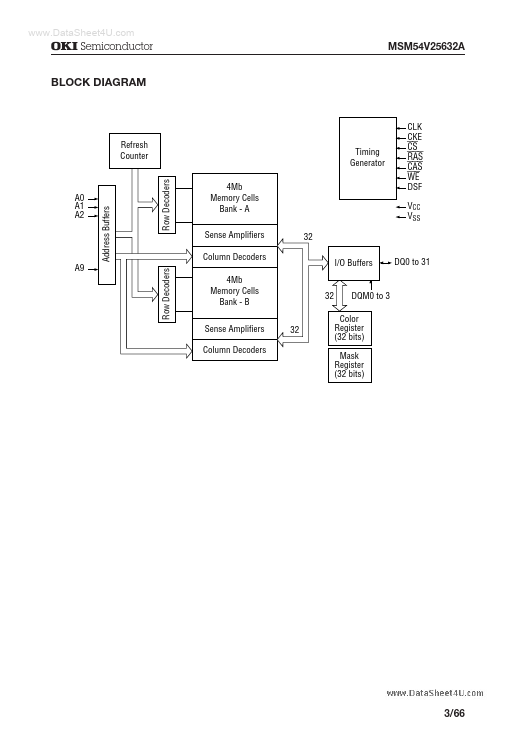

1999 MSM54V25632A Previous version: 1998 131,072-Word ¥ 32-Bit ¥ 2-Bank Synchronous Graphics RAM The MSM54V25632A is a synchronous graphics random access memory organized as 128 K words ¥ 32 bits ¥ 2 banks. This device can operate up to 100 MHz by using synchronous interface.

MSM54V25632A Key Features

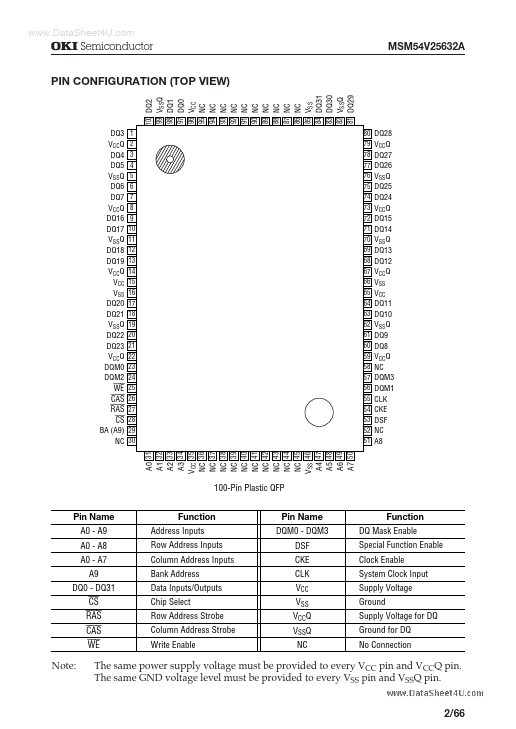

- 131,072 words

- 32 bits

- 2 banks memory

- Single 3.3 V ± 0.3 V power supply

- LVTTL patible inputs and outputs

- All input signals are latched at rising edge of system clock

- Auto precharge and controlled precharge

- Internal pipelined operation: column address can be changed every clock cycle

- Dual internal banks controlled by A9 (Bank Address: BA)

- Independent byte operation via DQM0 to DQM3