FDC6321C

FDC6321C is Dual N & P-Channel Digital FET manufactured by onsemi.

Dual, N & P-Channel, Digital FET

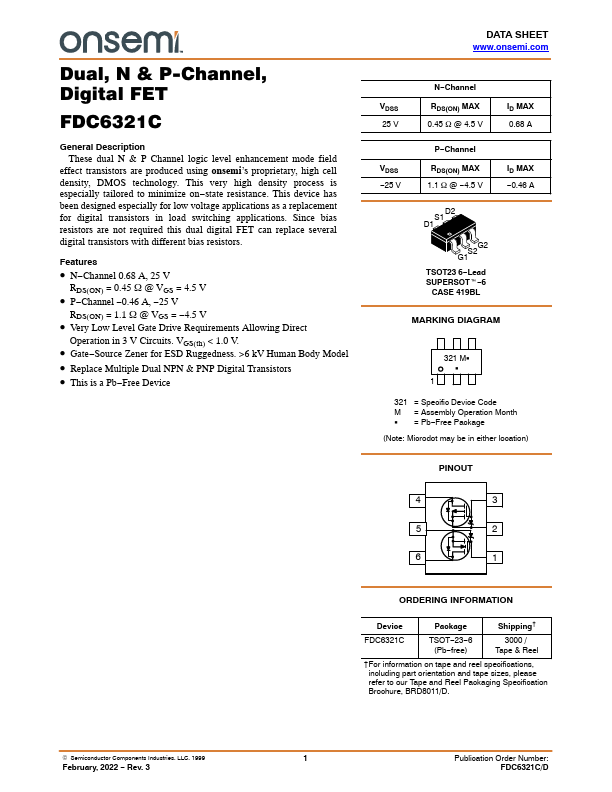

General Description These dual N & P Channel logic level enhancement mode field effect transistors are produced using onsemi’s proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on- state resistance. This device has been designed especially for low voltage applications as a replacement for digital transistors in load switching applications. Since bias resistors are not required this dual digital FET can replace several digital transistors with different bias resistors.

Features

- N- Channel 0.68 A, 25 V

RDS(ON) = 0.45 W @ VGS = 4.5 V

- P- Channel

- 0.46 A,

- 25 V

RDS(ON) = 1.1 W @ VGS =

-...