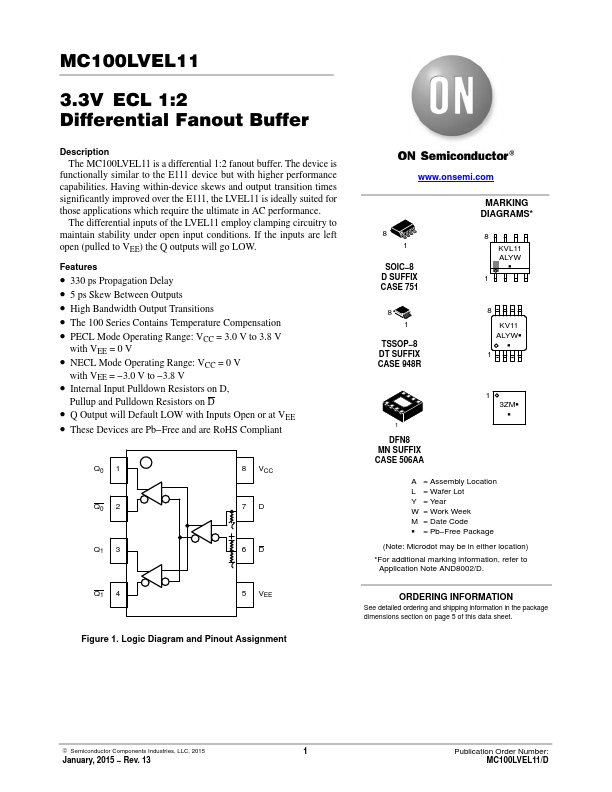

MC100LVEL11 Overview

The MC100LVEL11 is a differential 1:2 fanout buffer. The device is functionally similar to the E111 device but with higher performance capabilities. Having within-device skews and output transition times significantly improved over the E111, the LVEL11 is ideally suited for those applications which require the ultimate in AC performance.

MC100LVEL11 Key Features

- 330 ps Propagation Delay

- 5 ps Skew Between Outputs

- High Bandwidth Output Transitions

- The 100 Series Contains Temperature pensation

- PECL Mode Operating Range: VCC = 3.0 V to 3.8 V

- NECL Mode Operating Range: VCC = 0 V

- Internal Input Pulldown Resistors on D

- Q Output will Default LOW with Inputs Open or at VEE

- These Devices are Pb-Free and are RoHS pliant

- For additional marking information, refer to Application Note AND8002/D