Datasheet Summary

3.3 V/5 V ECL D Flip-Flop with Reset and Differential Clock

MC10EP51, MC100EP51

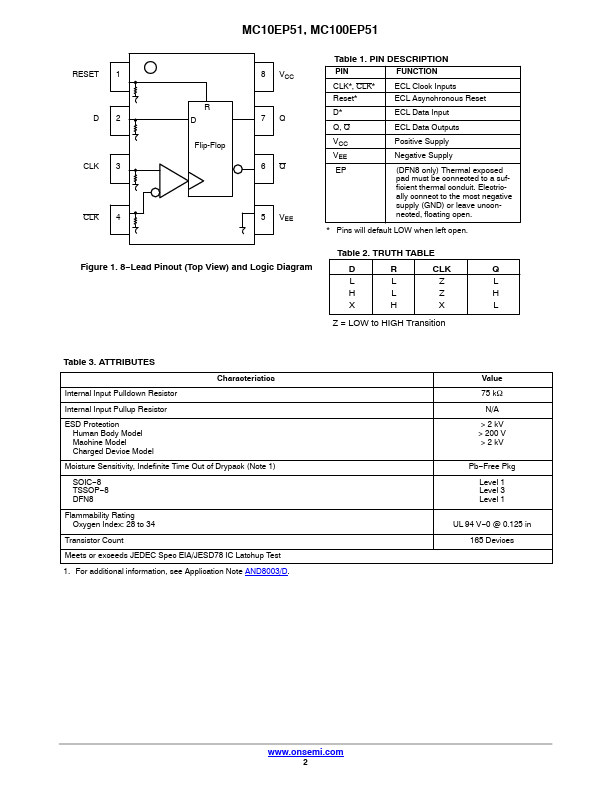

Description The MC10/100EP51 is a differential clock D flip- flop with reset.

The device is functionally equivalent to the EL51 and LVEL51 devices.

The reset input is an asynchronous, level triggered signal. Data enters the master portion of the flip- flop when the clock is LOW and is transferred to the slave, and thus the outputs, upon a positive transition of the clock. The differential clock inputs of the EP51 allow the device to be used as a negative edge triggered flip-flop.

The differential input employs clamp circuitry to maintain stability under open input conditions. When left open, the CLK input will...