PE3336 Description

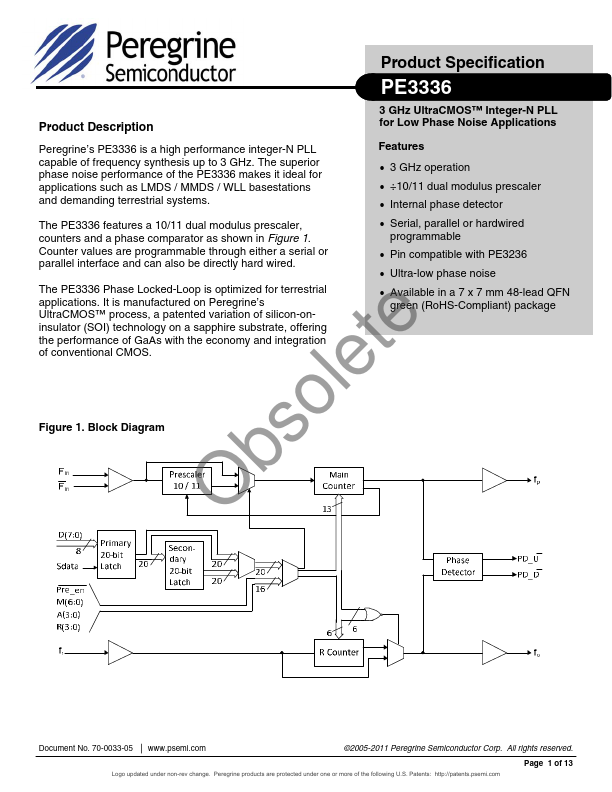

3 GHz UltraCMOS™ Integer-N PLL for Low Phase Noise Applications Peregrine’s PE3336 is a high performance integer-N PLL capable of frequency synthesis up to 3 GHz. The superior phase noise performance of the PE3336 makes it ideal for applications such as LMDS / MMDS / WLL basestations and demanding terrestrial systems.

PE3336 Key Features

- 3 GHz operation - ÷10/11 dual modulus prescaler - Internal phase detector

- Serial, parallel or hardwired programmable

- Pin patible with PE3236

- Ultra-low phase noise