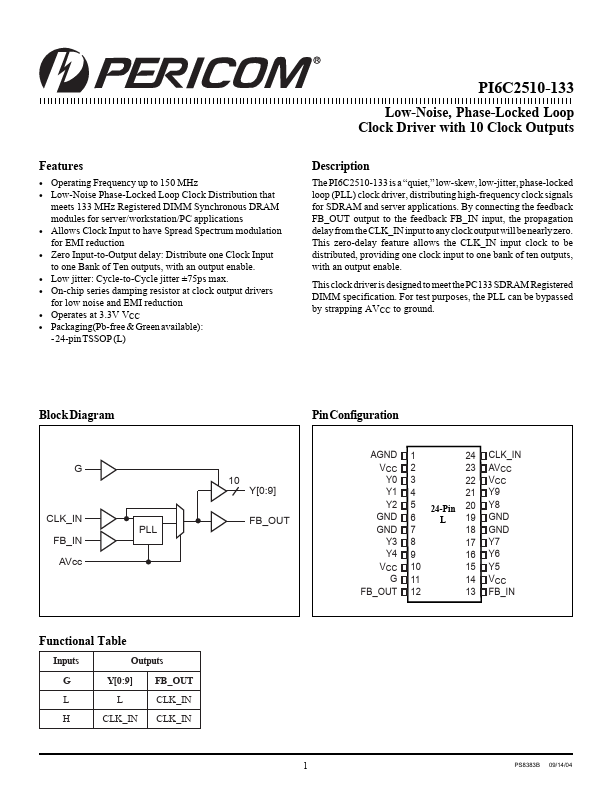

PI6C2510-133 Description

The PI6C2510-133 is a “quiet,” low-skew, low-jitter, phase-locked loop (PLL) clock driver, distributing high-frequency clock signals for SDRAM and server applications. By connecting the feedback FB_OUT output to the feedback FB_IN input, the propagation delay from the CLK_IN input to any clock output will be nearly zero.

PI6C2510-133 Key Features

- Description