Datasheet Summary

..

QL16x24B pASIC® 1 Family Very-High-Speed CMOS FPGA

Rev C pASIC HIGHLIGHTS Very High Speed

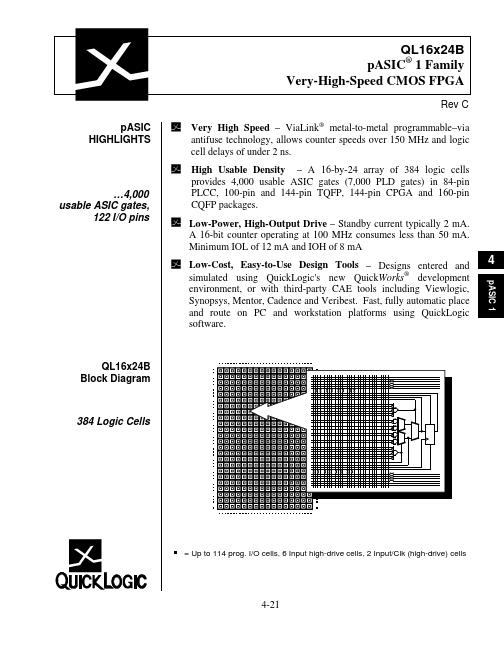

- ViaLink® metal-to-metal programmable- via antifuse technology, allows counter speeds over 150 MHz and logic cell delays of under 2 ns. High Usable Density

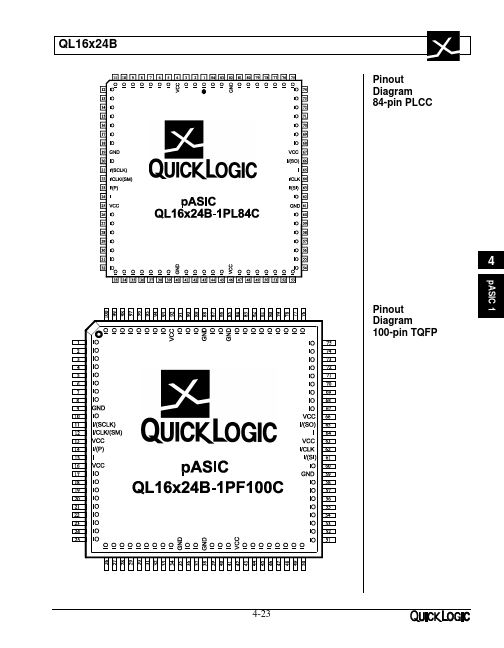

- A 16-by-24 array of 384 logic cells provides 4,000 usable ASIC gates (7,000 PLD gates) in 84-pin PLCC, 100-pin and 144-pin TQFP, 144-pin CPGA and 160-pin CQFP packages. Low-Power, High-Output Drive

- Standby current typically 2 mA. A 16-bit counter operating at 100 MHz consumes less than 50 mA. Minimum IOL of 12 mA and IOH of 8 mA Low-Cost, Easy-to-Use Design Tools

- Designs entered and simulated using QuickLogic's new...