70V05L

Description

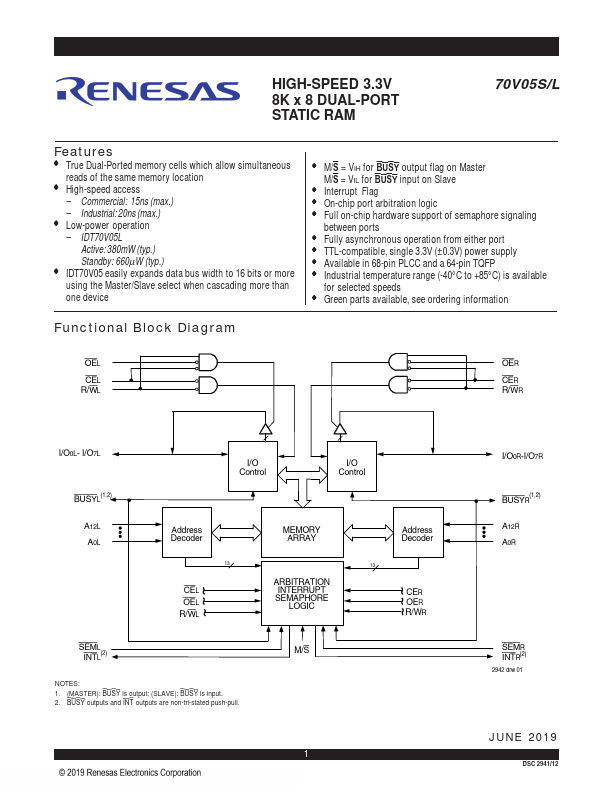

The IDT70V05 is a high-speed 8K x 8 Dual-Port Static RAM.

Key Features

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High-speed access - mercial: 15ns (max.) - Industrial: 20ns (max.)

- Low-power operation - IDT70V05L Active: 380mW (typ.) Standby: 660μW (typ.)

- IDT70V05 easily expands data bus width to 16 bits or more using the Master/Slave select when cascading more than one device

- M/S = VIH for BUSY output flag on Master M/S = VIL for BUSY input on Slave

- Interrupt Flag

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- Available in 68-pin PLCC and a 64-pin TQFP