70V7519S Overview

Key Specifications

Package: BGA

Mount Type: Surface Mount

Pins: 256

Operating Voltage: 3.3 V

Key Features

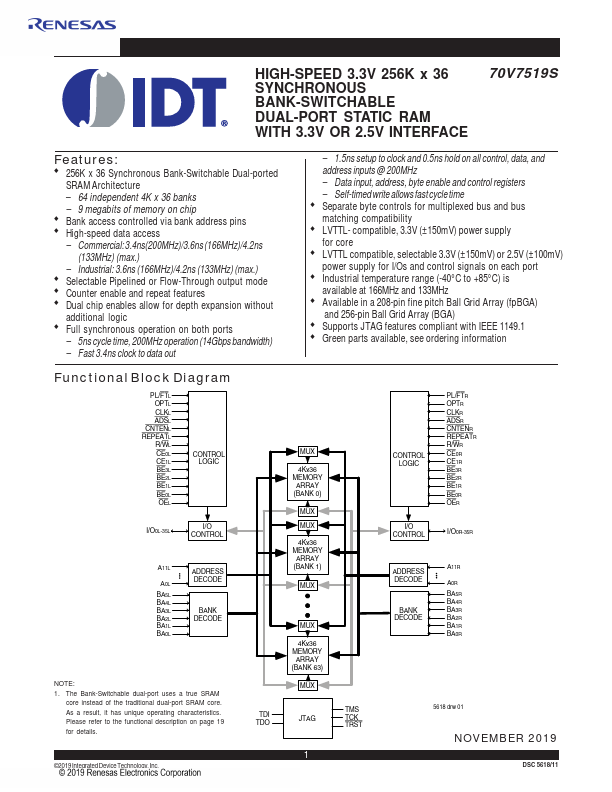

- 256K x 36 Synchronous Bank-Switchable Dual-ported SRAM Architecture – 64 independent 4K x 36 banks – 9 megabits of memory on chip

- Bank access controlled via bank address pins

- Selectable Pipelined or Flow-Through output mode

- Counter enable and repeat features

- Dual chip enables allow for depth expansion without additional logic