72V3690 Datasheet Text

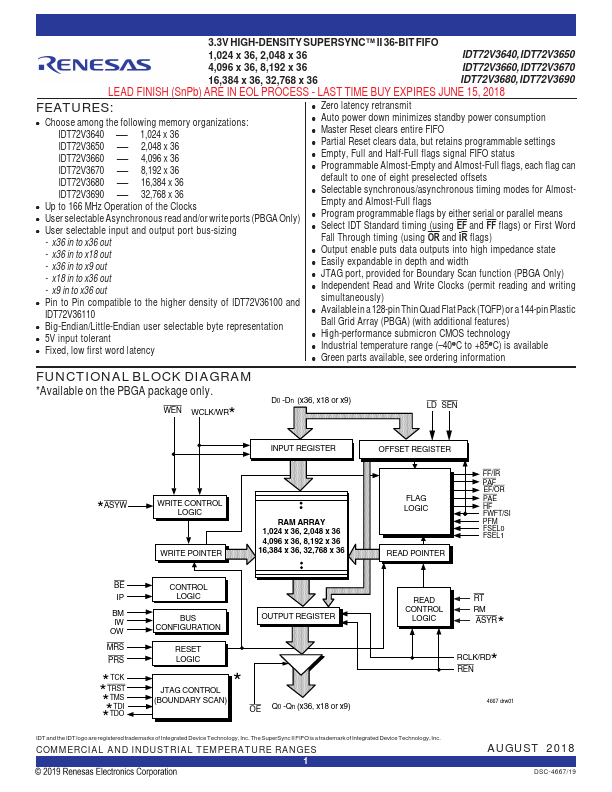

3.3V HIGH-DENSITY SUPERSYNC™ II 36-BIT FIFO

1,024 x 36, 2,048 x 36

IDT72V3640, IDT72V3650

4,096 x 36, 8,192 x 36

IDT72V3660, IDT72V3670

16,384 x 36, 32,768 x 36

IDT72V3680, IDT72V3690

LEAD FINISH (SnPb) ARE IN EOL PROCESS

- LAST TIME BUY EXPIRES JUNE 15, 2018

Features

:

- Choose among the following memory organizations:mercial

IDT72V3640 ⎯ 1,024 x 36 IDT72V3650 ⎯ 2,048 x 36 IDT72V3660 ⎯ 4,096 x 36 IDT72V3670 ⎯ 8,192 x 36 IDT72V3680 ⎯ 16,384 x 36 IDT72V3690 ⎯ 32,768 x 36

- Up to 166 MHz Operation of the Clocks

- User selectable Asynchronous read and/or write ports (PBGA Only)

- User selectable input and output port bus-sizing

- x36 in to x36 out

- x36 in to x18 out

- x36 in to x9 out

- x18 in to x36 out

- x9 in to x36 out

- Pin to Pin patible to the higher density of IDT72V36100 and

IDT72V36110

- Big-Endian/Little-Endian user selectable byte representation

- 5V input tolerant

- Fixed, low first word latency

- Zero latency retransmit

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings...