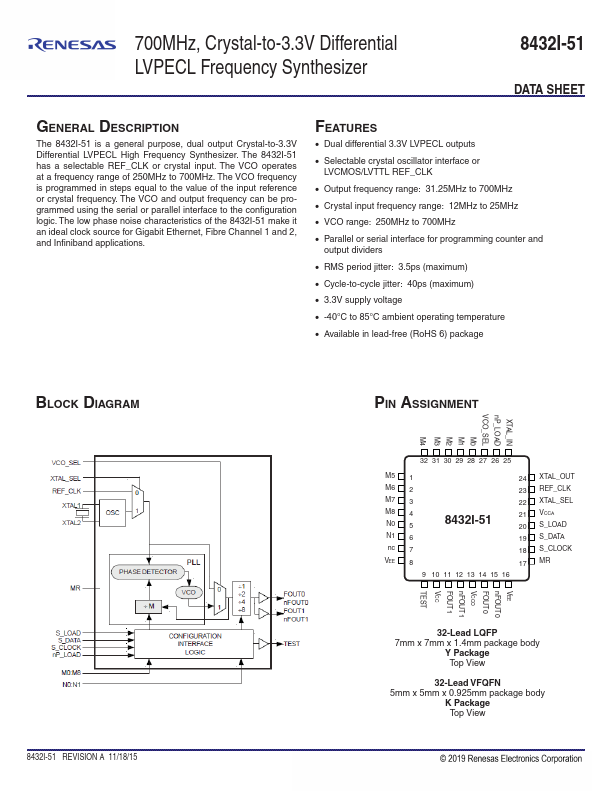

8432I-51 Overview

The 8432I-51 is a general purpose, dual output Crystal-to-3.3V Differential LVPECL High Frequency Synthesizer. The 8432I-51 has a selectable REF_CLK or crystal input. The VCO operates at a frequency range of 250MHz to 700MHz.

8432I-51 Key Features

- Dual differential 3.3V LVPECL outputs

- Selectable crystal oscillator interface or

- Output frequency range: 31.25MHz to 700MHz

- Crystal input frequency range: 12MHz to 25MHz

- VCO range: 250MHz to 700MHz

- Parallel or serial interface for programming counter and

- RMS period jitter: 3.5ps (maximum)

- Cycle-to-cycle jitter: 40ps (maximum)

- 3.3V supply voltage

- 40°C to 85°C ambient operating temperature