Datasheet Summary

Synchronization Management Unit

8A34001 Datasheet

Overview

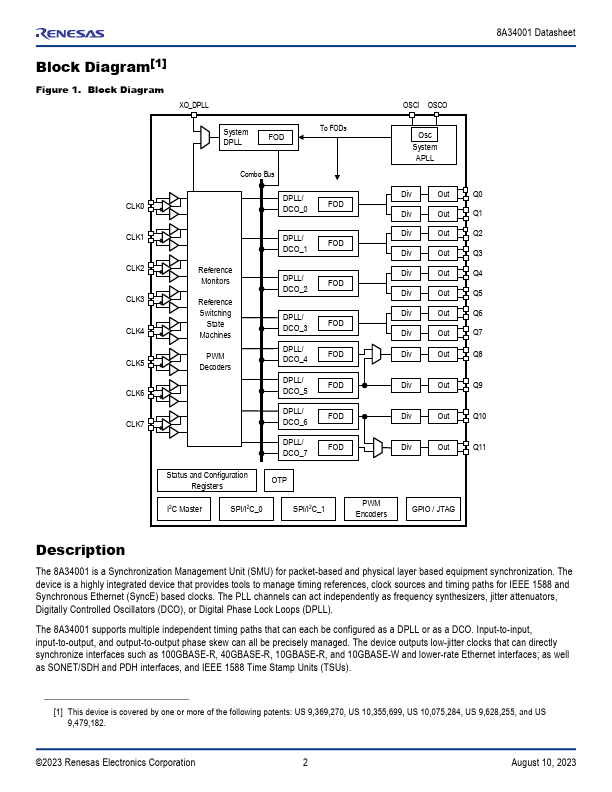

The 8A34001 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources, and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The PLL channels can act independently as frequency synthesizers, jitter attenuators, Digitally Controlled Oscillators (DCO), or Digital Phase Lock Loops (DPLL).

Optional clock recovery filter/servo software is available under license from Renesas for use with the 8A34001. The filter/servo software is designed to suppress the effects of Packet Delay Variation (PDV) on packet based timing signals

- it can be used with protocol stacks for IEEE 1588...