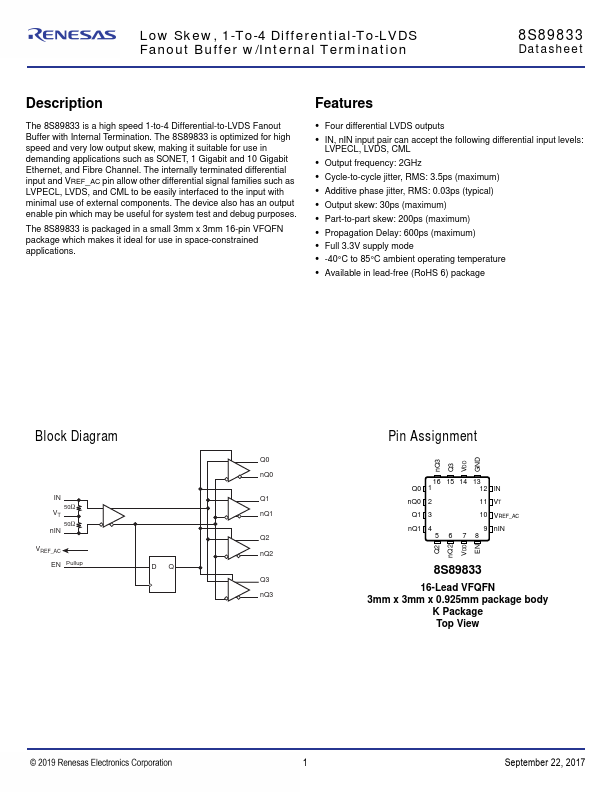

8S89833

Description

The 8S89833 is a high speed 1-to-4 Differential-to-LVDS Fanout Buffer with Internal Termination.

Key Features

- Four differential LVDS outputs

- IN, nIN input pair can accept the following differential input levels

- Output frequency: 2GHz

- Cycle-to-cycle jitter, RMS: 3.5ps (maximum)

- Additive phase jitter, RMS: 0.03ps (typical)

- Output skew: 30ps (maximum)

- Part-to-part skew: 200ps (maximum)

- Propagation Delay: 600ps (maximum)

- Full 3.3V supply mode

- 40°C to 85°C ambient operating temperature