8V19N850D

8V19N850D is Radio Unit Clock Synchronizer and Converter Clock Generator manufactured by Renesas.

Description

The 8V19N850 is a fully integrated Radio Unit Clock Synchronizer and Converter Clock Generator designed as a high-performance clock solution for phase/frequency synchronization and signal conditioning of wireless base station radio equipment. The device supports JESD204B/C subclass 0 and 1 device clocks and SYSREF synchronization for converters.

The 8V19N850 supports two independent frequency domains: one that can be used for the digital clock (Ethernet and FEC rates) domain with four outputs, and the device clock (RF-PLL) domain with 12 outputs. The Ethernet domain generates frequencies from two independent APLLs for flexibility; the outputs of the RF clock domain generate very low phase noise clocks for ADC/DAC circuits.

From the integrated RF-PLL, the device supports the clock generation of high-frequency device clocks for driving ADC/DAC devices low-frequency synchronization signals (SYSREF).

A dual DPLL front-end architecture supports any frequency translation. Each DPLL provides a programmable bandwidth and a DCO function for real-time frequency/phase adjustments. The DPLLs can lock on 1PPS input signals and establish lock within 100s or less. Frequency information can be applied from DPLL-0 to DPLL-1 and vice versa to enable the bining of the frequency characteristics of two references (bo-mode).

The 8V19N850 is configured through a pin-mapped I3CSM (including legacy I2C) and 3/4-wire SPI interface. I2C with master capabilities reads a default configuration from an external ROM device. GPIO ports can be configured for reporting and controlling purposes.

Applications

- Wireless infrastructure 5G radio

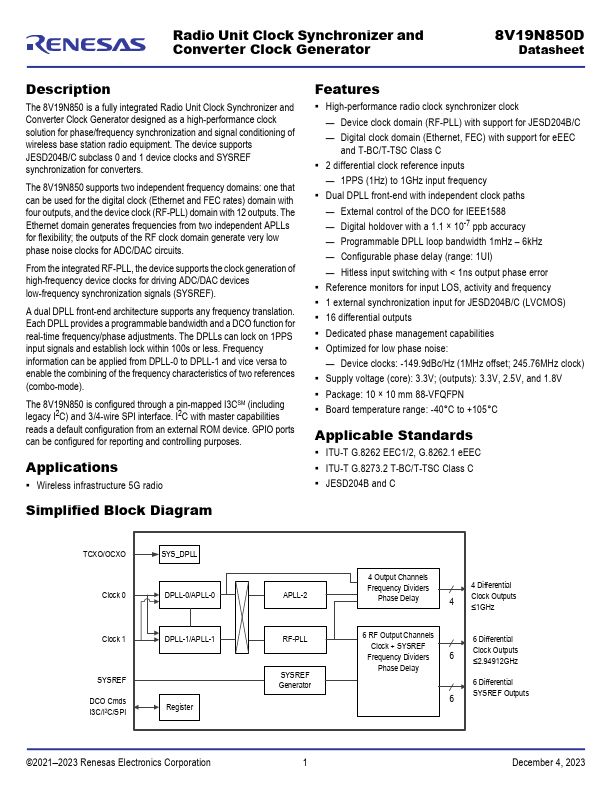

Simplified Block Diagram

Features

- High-performance radio clock synchronizer clock

- Device clock domain (RF-PLL) with support for JESD204B/C

- Digital clock domain (Ethernet, FEC) with support for e EEC and T-BC/T-TSC Class C

- 2 differential clock reference inputs

- 1PPS (1Hz) to 1GHz input frequency

- Dual DPLL front-end with independent clock...