9DML4493A

9DML4493A is 4:4 Clock MUX manufactured by Renesas.

Description

The 9DML4493A is a 4-input, 4-output clock multiplexer. It can also operate as a dual 2-input, 2-output clock multiplexer. It has very low additive phase jitter and is suitable for all PCIe data rates. The device supports today's plex system power sequencing requirements with Power Down Tolerant and Flexible Power Sequencing features

.

Typical Applications

- Servers

- Storage

- Networking

- High-Performance puting

- Accelerators

Key Specifications

- Additive phase jitter:

- 8fs RMS typical (PCIe Gen6 CC at 100MHz)

- 66fs RMS typical (12k Hz- 20MHz at 156.25M)

- Supports mon Clocked (CC) and IR (SRIS, SRNS) timing architectures.

- Propagation delay < 1.2ns typical

Features

- Four differential inputs support LVPECL, LVDS, HCSL or LVCMOS reference clocks

- Flexible Power Sequencing (FPS) ensures good behavior when powered up without input clock, or when the input clock is present without power

- Power-Down Tolerant (PDT) inputs: CLK_SEL_tri, OE pins, IOA_tri, IOB_tri, ZOUTSEL may be driven when the 9DML4493 is not powered up

- Accepts input frequencies ranging from 1PPS (1Hz) to 350MHz

- Configured via pin straps

- no serial bus needed

- Pin-selectable 100Ω or 85Ω differential output impedance

- Three pin-selectable output amplitudes per bank

- Pin-selectable 4:4 mode or dual 2:2 MUX modes

- Glitch-free output enable pins for each output

- Spread-spectrum tolerant

- Voltage supply of 1.8V, 2.5V, or 3.3V

- -40°C to +85°C ambient operating temperature

- 5 × 5 mm 32-VFQFPN package

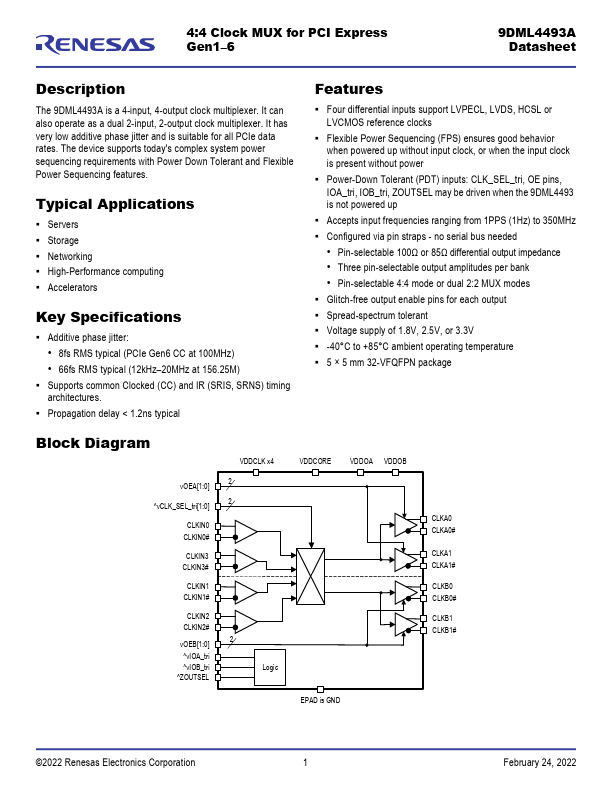

Block Diagram v OEA[1:0]

^v CLK_SEL_tri[1:0]

CLKIN0 CLKIN0#

CLKIN3 CLKIN3#

CLKIN1 CLKIN1#

CLKIN2 CLKIN2# v OEB[1:0] ^v I OA_tri ^v I OB_tri ^ZOUTSEL

VDDCLK x4 2 2

2 Logic

VDDCORE VDDOA VDDOB EPAD is GND

CLKA0...