EL7222 Description

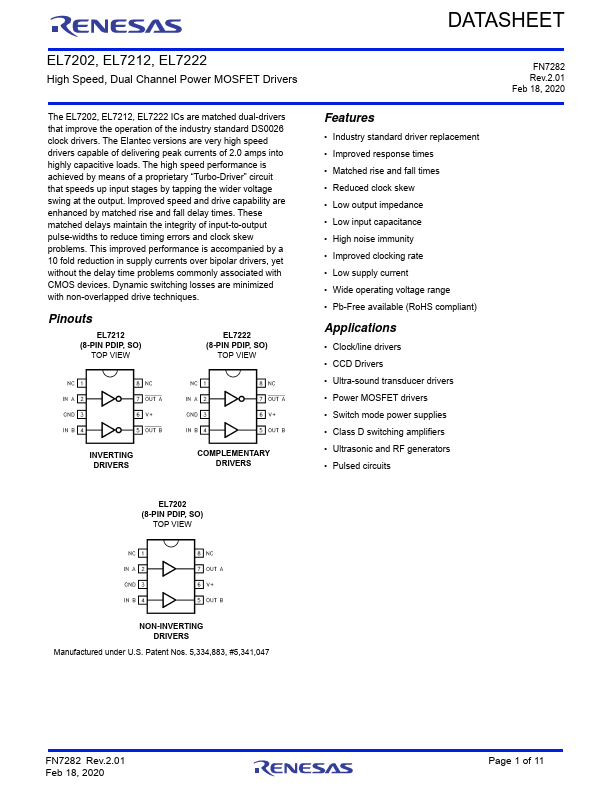

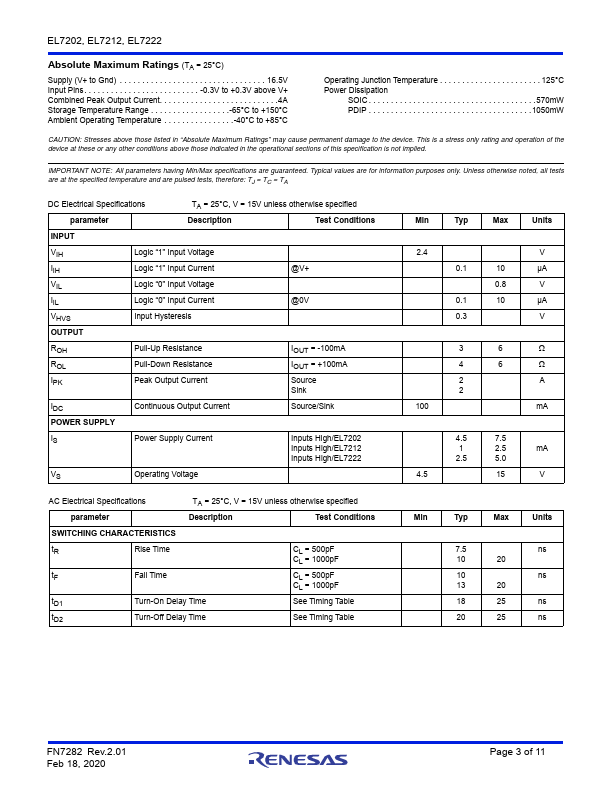

DATASHEET EL7202, EL7212, EL7222 High Speed, Dual Channel Power MOSFET Drivers The EL7202, EL7212, EL7222 ICs are matched dual-drivers that improve the operation of the industry standard DS0026 clock drivers. The Elantec versions are very high speed drivers capable of delivering peak currents of 2.0 amps into highly capacitive loads. The high speed performance is achieved by means of a proprietary “Turbo-Driver”...

EL7222 Key Features

- Industry standard driver replacement

- Improved response times

- Matched rise and fall times

- Reduced clock skew

- Low output impedance

- Low input capacitance

- High noise immunity

- Improved clocking rate

- Low supply current

- Wide operating voltage range