HD74HC165

HD74HC165 is Parallel-load 8-bit Shift Register manufactured by Renesas.

Parallel-load 8-bit Shift Register

REJ03D0581-0300 Rev.3.00

Jan 31, 2006

Description

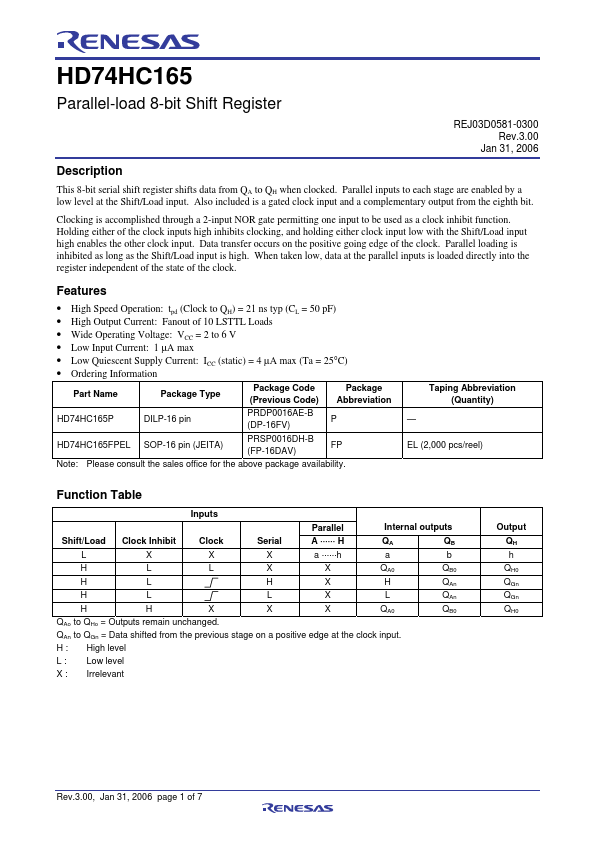

This 8-bit serial shift register shifts data from QA to QH when clocked. Parallel inputs to each stage are enabled by a low level at the Shift/Load input. Also included is a gated clock input and a plementary output from the eighth bit.

Clocking is acplished through a 2-input NOR gate permitting one input to be used as a clock inhibit function. Holding either of the clock inputs high inhibits clocking, and holding either clock input low with the Shift/Load input high enables the other clock input. Data transfer occurs on the positive going edge of the clock. Parallel loading is inhibited...