HD74HC165 Overview

Description

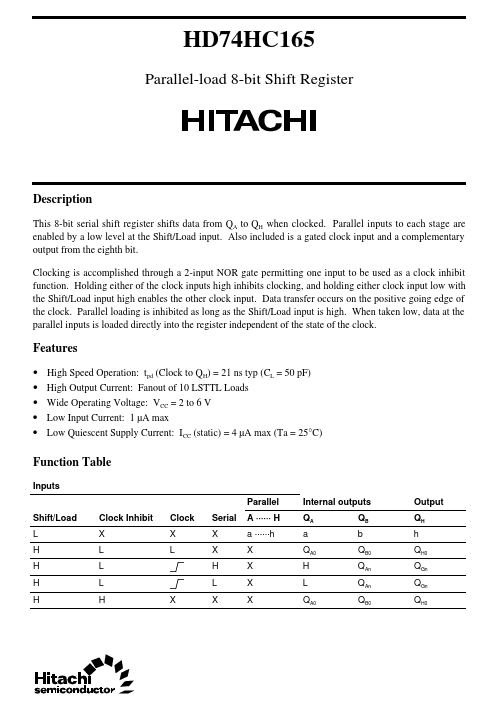

This 8-bit serial shift register shifts data from QA to QH when clocked. Parallel inputs to each stage are enabled by a low level at the Shift/Load input.

Key Features

- 0.5 1.35 1.8

- 0.1 0.1 0.1 0.33 0.33 ±1.0 40 µA µA I OL = 4 mA I OL = 5.2 mA Vin = VCC or GND Vin = VCC or GND, Iout = 0 µA V I OH = –4 mA I OH = –5.2