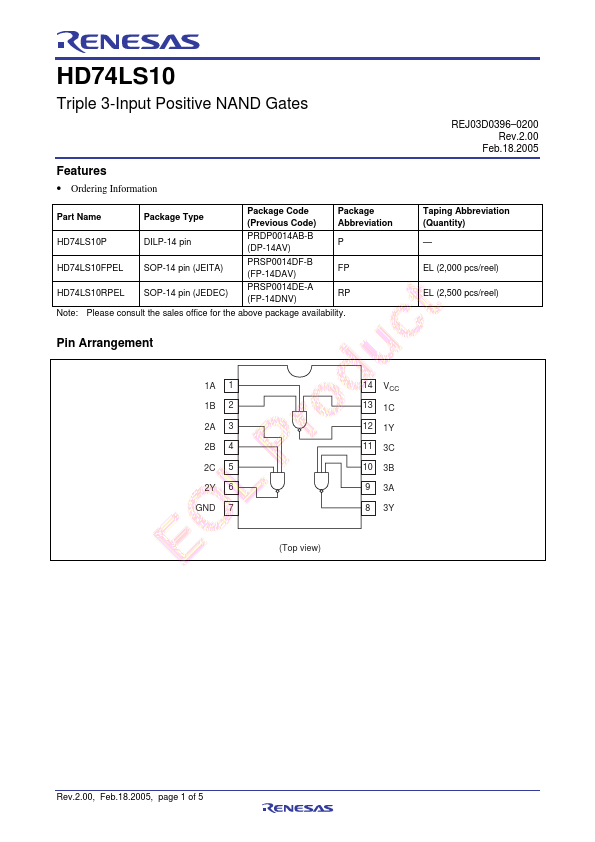

| Part | HD74LS10 |

|---|---|

| Description | Triple 3-Input Positive NAND Gates |

| Manufacturer | Renesas |

| Size | 154.92 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS109 | Hitachi Semiconductor | Dual J-K Positive-edge-triggered Flip-Flops |

| HD74LS109A | Hitachi Semiconductor | Dual J-K Positive-edge-triggered Flip-Flops |

| HD74LS10 | Hitachi Semiconductor | Triple 3-input Positive NAND Gates |

| HD74LS107A | Hitachi Semiconductor | Dual J-K Negative-edge-triggered Flip-Flops |

| HD74LS138 | Hitachi Semiconductor | 3-Line-to-8-Line Decoders/Demultiplexers |