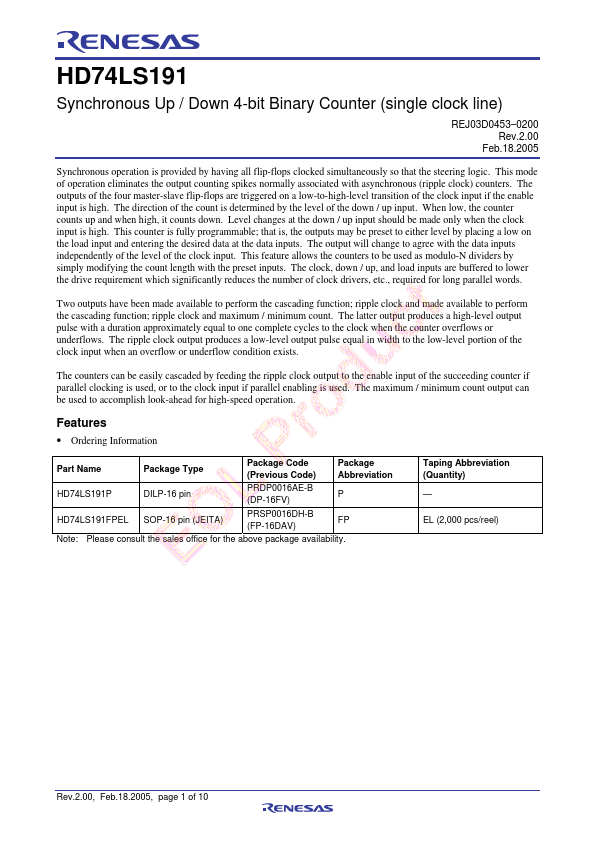

| Part | HD74LS191P |

|---|---|

| Description | Synchronous Up / Down 4-bit Binary Counter |

| Manufacturer | Renesas |

| Size | 263.97 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS191 | Hitachi Semiconductor | Synchronous Up/Down 4-bit Binary Counters |

| HD74LS190 | Hitachi Semiconductor | Synchronous Up/Down Decade Counters |

| HD74LS193 | Hitachi Semiconductor | Synchronous Up/Down 4-bit Binary Counters |

| HD74LS194A | Hitachi Semiconductor | 4-bit Bidirectional Universal Shift Registers |

| HD74LS192 | Hitachi Semiconductor | Synchronous Up/Down Decade Counters |