ICS8516I

ICS8516I is Clock Distribution manufactured by Renesas.

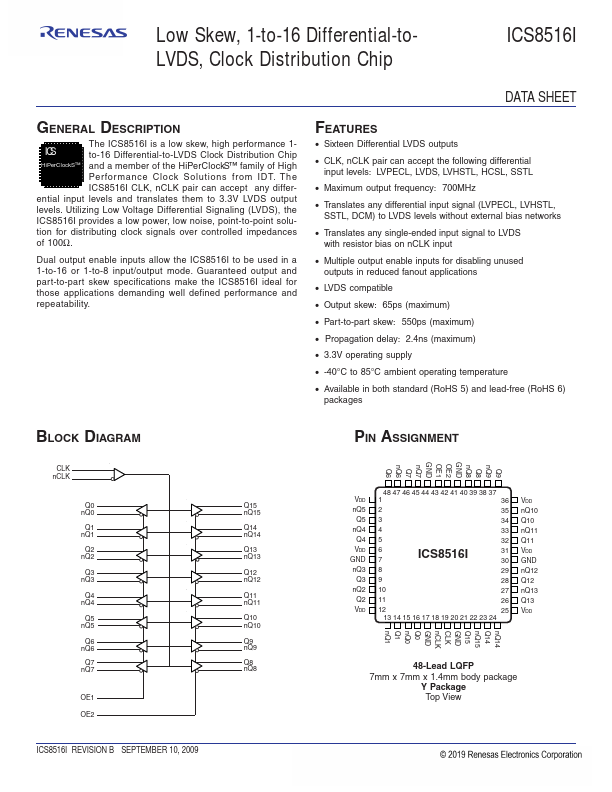

Low Skew, 1-to-16 Differential-toLVDS, Clock Distribution Chip

DATA SHEET

GENERAL DESCRIPTION

The ICS8516I is a low skew, high performance 1-

ICS to-16 Differential-to-LVDS Clock Distribution Chip

HiPerClockS™ and a member of the HiPerClockS™ family of High

Perfor mance Clock Solutions from IDT. The

ICS8516I CLK, nCLK pair can accept any differ- ential input levels and translates them to 3.3V LVDS output levels. Utilizing Low Voltage Differential Signaling (LVDS), the

ICS8516I provides a low power, low noise, point-to-point solu- tion for distributing clock signals over controlled impedances of 100Ω.

Dual output enable inputs allow the ICS8516I to be used in a...