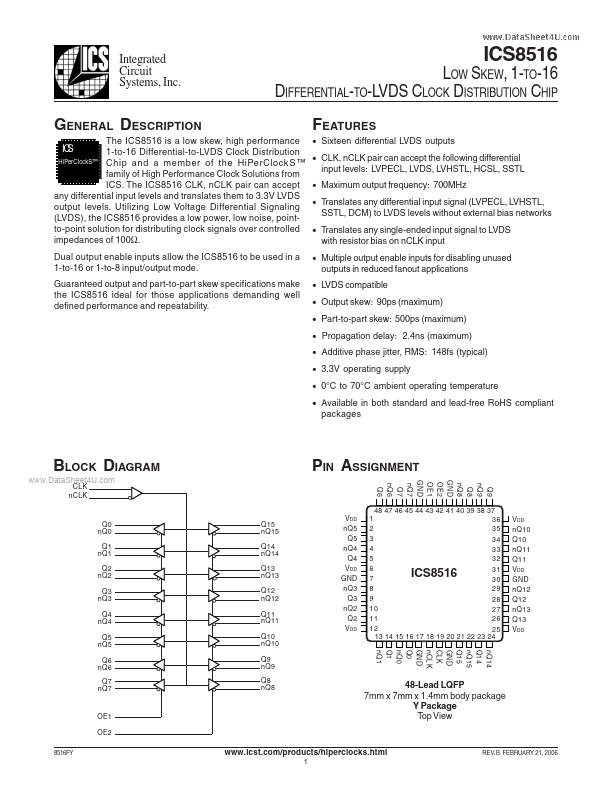

Datasheet Summary

Integrated Circuit Systems, Inc.

LOW SKEW, 1-TO-16 DIFFERENTIAL-TO-LVDS CLOCK DISTRIBUTION CHIP

Features

- Sixteen differential LVDS outputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

- Translates any single-ended input signal to LVDS with resistor bias on nCLK input

- Multiple output enable inputs for disabling unused outputs in reduced fanout applications

- LVDS patible

- Output skew: 90ps (maximum)

- Part-to-part skew: 500ps (maximum)

- Propagation delay: 2.4ns...