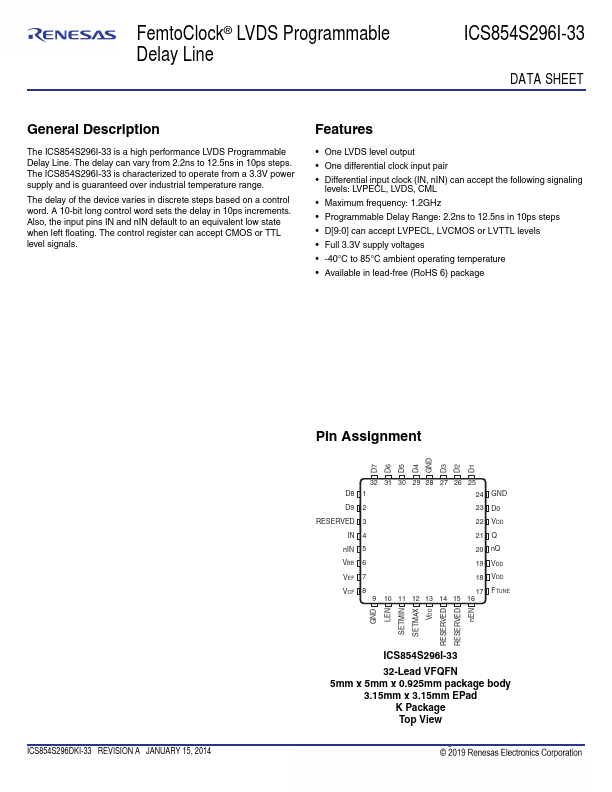

ICS854S296I-33 Description

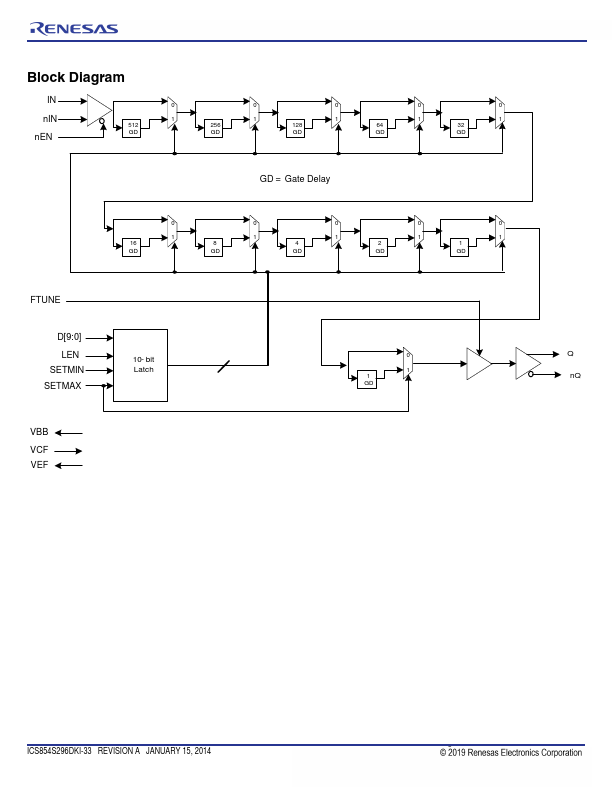

The ICS854S296I-33 is a high performance LVDS Programmable Delay Line. The delay can vary from 2.2ns to 12.5ns in 10ps steps. The ICS854S296I-33 is characterized to operate from a 3.3V power supply and is guaranteed over industrial temperature range.

ICS854S296I-33 Key Features

- One LVDS level output

- One differential clock input pair

- Differential input clock (IN, nIN) can accept the following signaling

- Maximum frequency: 1.2GHz

- Programmable Delay Range: 2.2ns to 12.5ns in 10ps steps

- D[9:0] can accept LVPECL, LVCMOS or LVTTL levels

- Full 3.3V supply voltages

- 40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package