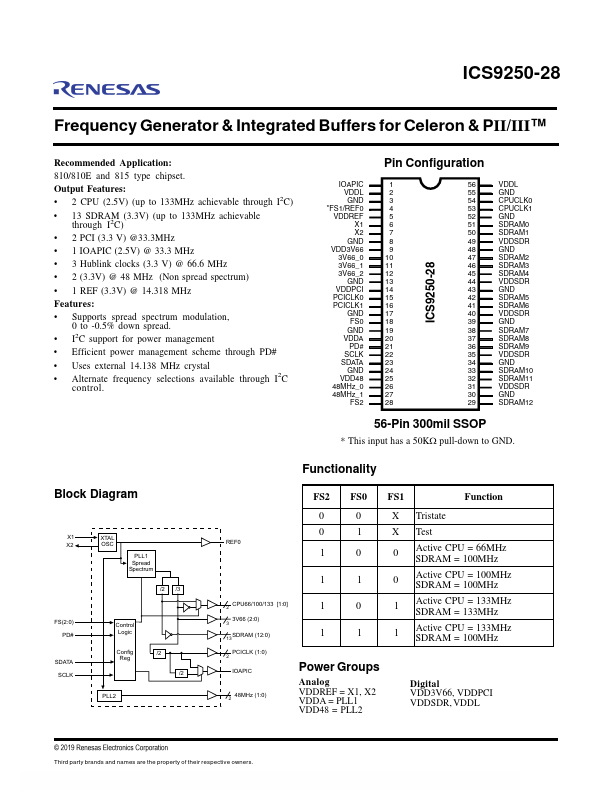

ICS9250-28 Overview

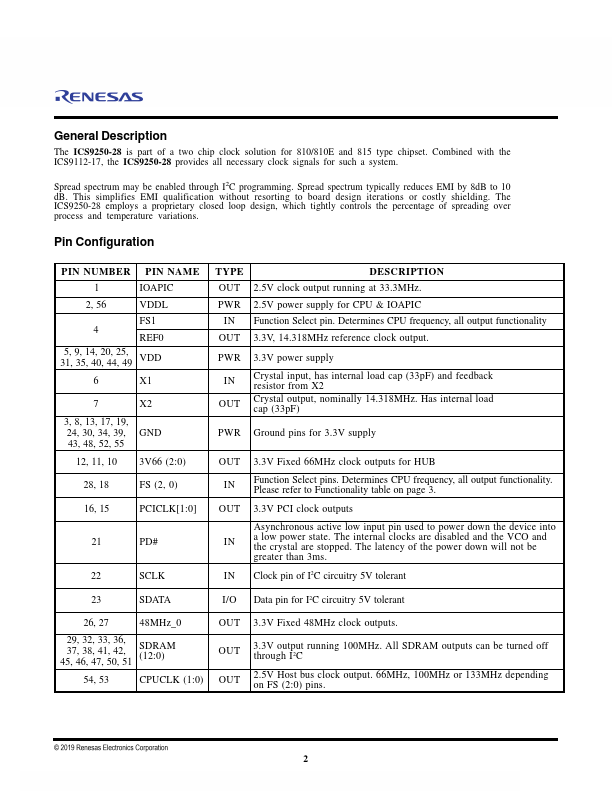

The ICS9250-28 is part of a two chip clock solution for 810/810E and 815 type chipset. bined with the ICS9112-17, the ICS9250-28 provides all necessary clock signals for such a system. Spread spectrum may be enabled through I2C programming.

ICS9250-28 Key Features

- 2 CPU (2.5V) (up to 133MHz achievable through I2C)

- 13 SDRAM (3.3V) (up to 133MHz achievable

- 2 PCI (3.3 V) @33.3MHz

- 1 IOAPIC (2.5V) @ 33.3 MHz

- 3 Hublink clocks (3.3 V) @ 66.6 MHz

- 2 (3.3V) @ 48 MHz (Non spread spectrum)

- 1 REF (3.3V) @ 14.318 MHz Features

- Supports spread spectrum modulation

- I2C support for power management

- Efficient power management scheme through PD#