IDT72V3670

IDT72V3670 is 3.3V HIGH-DENSITY 36-BIT FIFO manufactured by Renesas.

- Part of the IDT72V3640 comparator family.

- Part of the IDT72V3640 comparator family.

FEATURES

:

- Choose among the following memory organizations:mercial

IDT72V3640 ⎯ 1,024 x 36 IDT72V3650 ⎯ 2,048 x 36 IDT72V3660 ⎯ 4,096 x 36 IDT72V3670 ⎯ 8,192 x 36 IDT72V3680 ⎯ 16,384 x 36 IDT72V3690 ⎯ 32,768 x 36

- Up to 166 MHz Operation of the Clocks

- User selectable Asynchronous read and/or write ports (PBGA Only)

- User selectable input and output port bus-sizing

- x36 in to x36 out

- x36 in to x18 out

- x36 in to x9 out

- x18 in to x36 out

- x9 in to x36 out

- Pin to Pin patible to the higher density of IDT72V36100 and

IDT72V36110

- Big-Endian/Little-Endian user selectable byte representation

- 5V input tolerant

- Fixed, low first word latency

- Zero latency retransmit

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Empty, Full and Half-Full flags signal FIFO status

- Programmable Almost-Empty and Almost-Full flags, each flag can default to one of eight preselected offsets

- Selectable synchronous/asynchronous timing modes for Almost-

Empty and Almost-Full flags

- Program programmable flags by either serial or parallel means

- Select IDT Standard timing (using EF and FF flags) or First Word

Fall Through timing (using OR and IR flags)

- Output enable puts data outputs into high impedance state

- Easily expandable in depth and width

- JTAG port, provided for Boundary Scan function (PBGA Only)

- Independent Read and Write Clocks (permit reading and writing simultaneously)

- Available in a 128-pin Thin Quad Flat Pack (TQFP) or a 144-pin Plastic

Ball Grid Array (PBGA) (with additional features

)

- High-performance submicron CMOS technology

- Industrial temperature range (- 40°C to +85°C) is available

- Green parts available, see ordering information

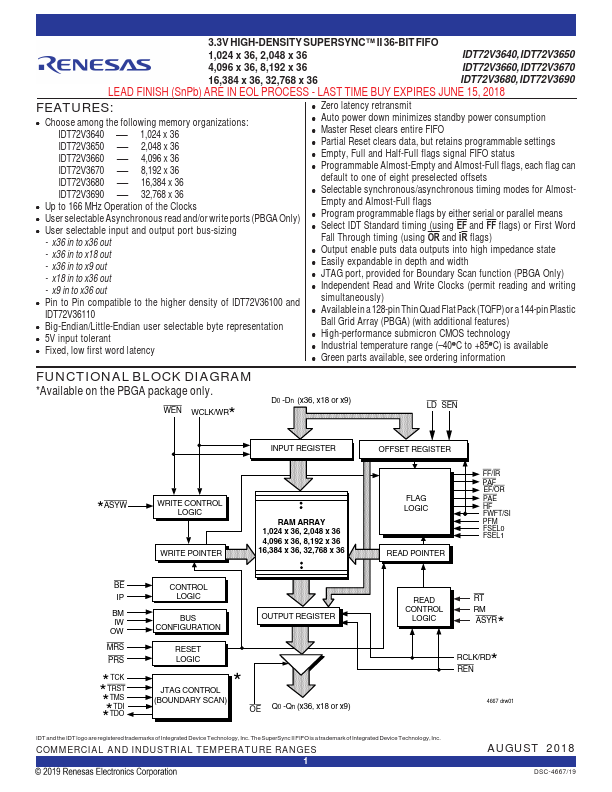

FUNCTIONAL BLOCK DIAGRAM

- Available on the PBGA package...