MK2304-2

Description

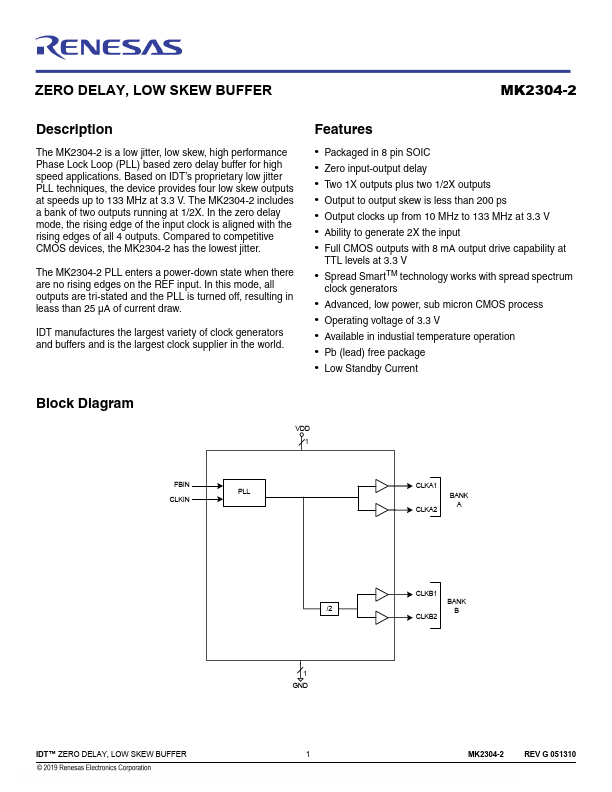

The MK2304-2 is a low jitter, low skew, high performance Phase Lock Loop (PLL) based zero delay buffer for high speed applications.

Key Features

- Packaged in 8 pin SOIC

- Zero input-output delay

- Two 1X outputs plus two 1/2X outputs

- Output to output skew is less than 200 ps

- Output clocks up from 10 MHz to 133 MHz at 3.3 V

- Ability to generate 2X the input

- Full CMOS outputs with 8 mA output drive capability at TTL levels at 3.3 V

- Spread SmartTM technology works with spread spectrum clock generators

- Advanced, low power, sub micron CMOS process

- Operating voltage of 3.3 V