R5F52305ADFP

Overview

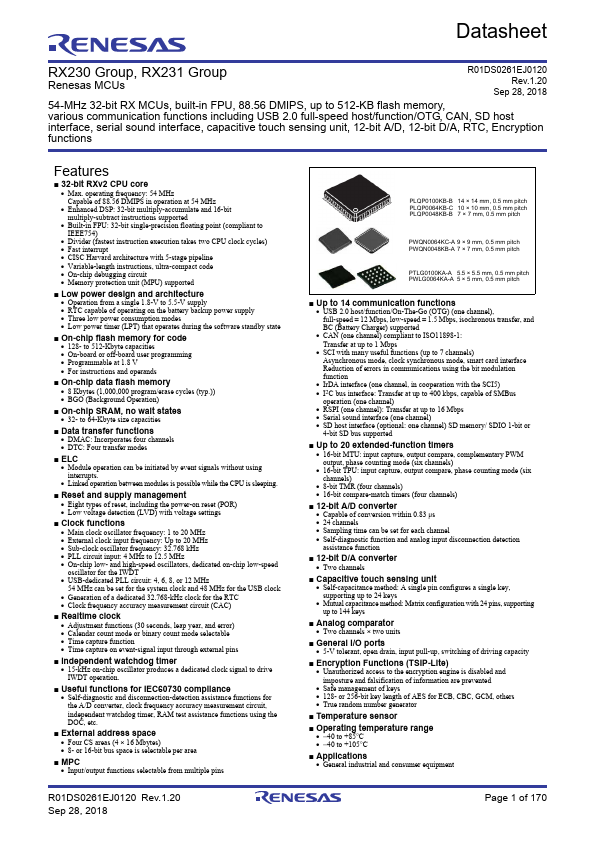

- 32-bit RXv2 CPU core

- Max. operating frequency: 54 MHz Capable of 88.56 DMIPS in operation at 54 MHz

- Enhanced DSP: 32-bit multiply-accumulate and 16-bit multiply-subtract instructions supported

- Built-in FPU: 32-bit single-precision floating point (compliant to IEEE754)

- Divider (fastest instruction execution takes two CPU clock cycles)

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length instructions, ultra-compact code

- On-chip debugging circuit

- Memory protection unit (MPU) supported