R5F566TFEDFP

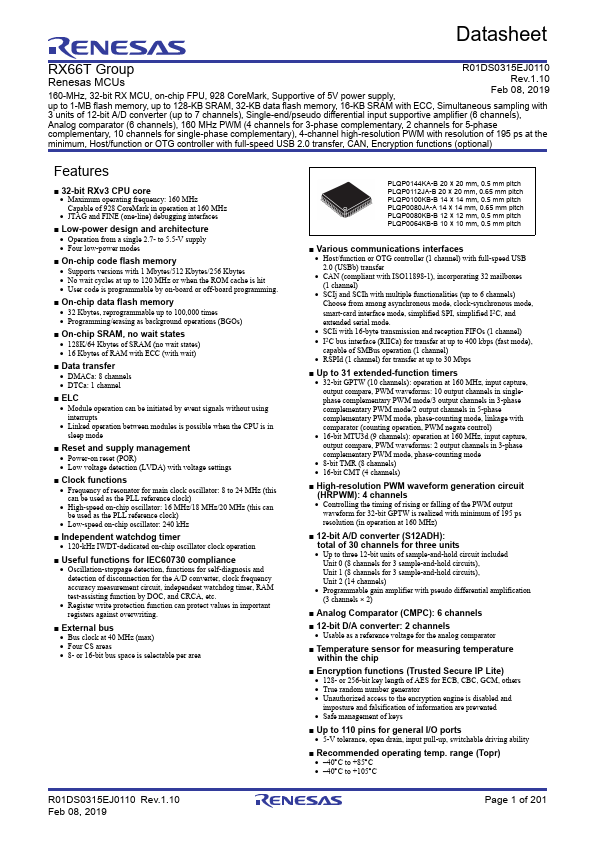

Key Features

- Low-power design and architecture Operation from a single 2.7- to 5.5-V supply Four low-power modes

- On-chip data flash memory 32 Kbytes, reprogrammable up to 100,000 times Programming/erasing as background operations (BGOs)

- On-chip SRAM, no wait states 128K/64 Kbytes of SRAM (no wait states) 16 Kbytes of RAM with ECC (with wait)

- Data transfer DMACa: 8 channels DTCa: 1 channel

- Reset and supply management Power-on reset (POR) Low voltage detection (LVDA) with voltage settings

- Independent watchdog timer 120-kHz IWDT-dedicated on-chip oscillator clock operation