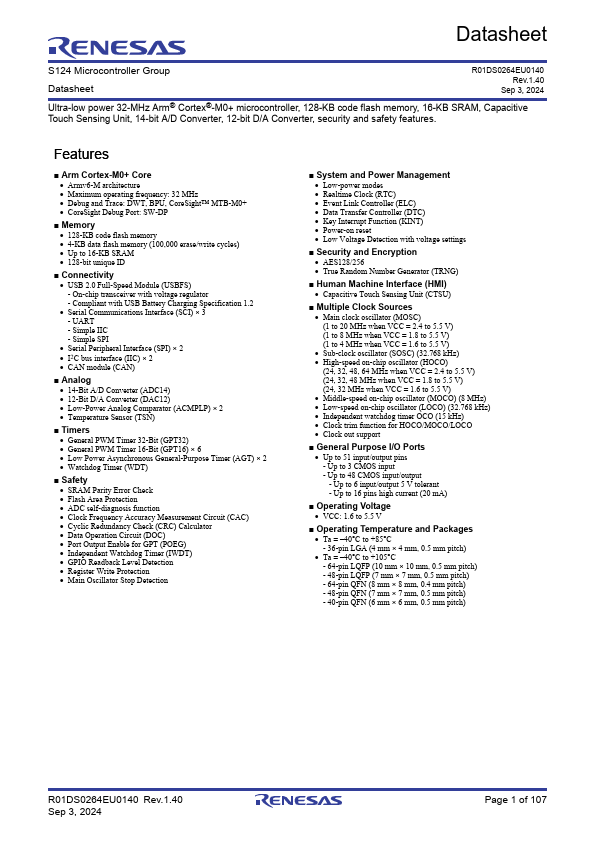

| Part | R7FS124763A01CFM |

|---|---|

| Description | Microcontroller |

| Category | Microcontroller |

| Manufacturer | Renesas |

| Size | 1.49 MB |

Pricing from 4.64 USD, available from Newark and Renesas.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Newark | 720 | 1+ : 4.64 USD 10+ : 3.76 USD 25+ : 3.54 USD 50+ : 3.44 USD |

View Offer |

| Renesas | 2206 | 1+ : 4.25 USD 10+ : 3.222 USD 25+ : 2.9648 USD 160+ : 2.60769 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HFDOM44P-xxxSx | Hanbit Electronics | 44Pin Flash Disk Module |

| HFDOM40B-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |

| CP2105 | Silicon Labs | SINGLE-CHIP USB TO DUAL UART BRIDGE |