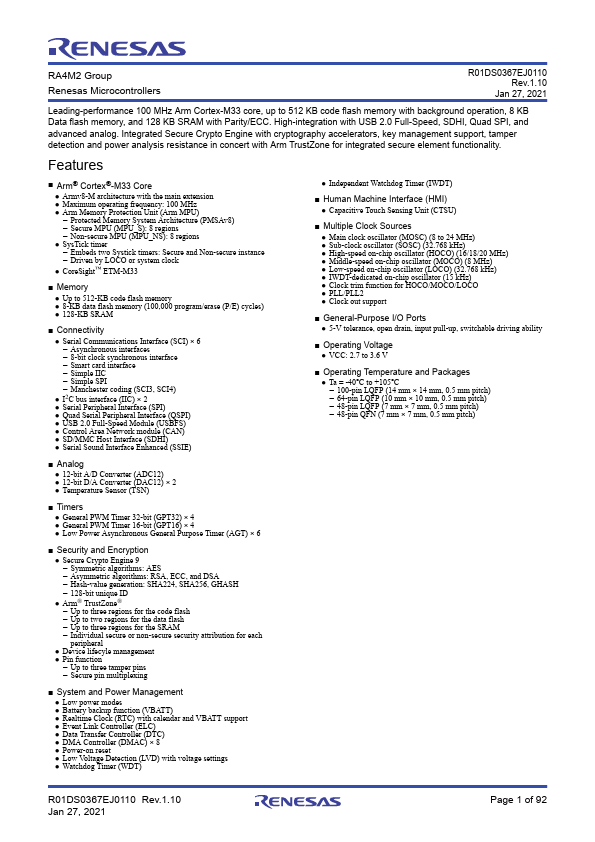

RA4M2

Features

- Arm® Cortex®-M33 Core

- Armv8-M architecture with the main extension

- Maximum operating frequency: 100 MHz

- Arm Memory Protection Unit (Arm MPU)

- Protected Memory System Architecture (PMSAv8)

- Secure MPU (MPU_S): 8 regions

- Non-secure MPU (MPU_NS): 8 regions

- Sys Tick timer

- Embeds two Systick timers: Secure and Non-secure instance

- Driven by LOCO or system clock

- Core Sight™ ETM-M33

- Memory

- Up to 512-KB code flash memory

- 8-KB data flash memory (100,000 program/erase (P/E) cycles)

- 128-KB SRAM

- Connectivity

- Serial munications Interface (SCI) × 6

- Asynchronous interfaces

- 8-bit clock synchronous interface

- Smart card interface

- Simple IIC

- Simple SPI

- Manchester coding (SCI3, SCI4)

- I2C bus interface (IIC) × 2

- Serial Peripheral Interface (SPI)

- Quad Serial Peripheral Interface (QSPI)

- USB 2.0 Full-Speed Module (USBFS)

- Control Area Network module (CAN)

- SD/MMC Host Interface (SDHI)

- Serial Sound Interface Enhanced (SSIE)

- Analog

- 12-bit A/D...